Устройство синхронизации

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii) 5537 37

Совз Советских

Социалистических

Реслублнк (61) Дополнительное к авт. свид-ву (22) Заявлено 04.09.74 (21) 2062131/21 с присоединением заявки № (23) Приоритет

Опубликовано 05.04.77. Бюллетень № 13

Дата опубликования описания 13.06.77 (51) М. Кл. Н 03К 5/156

Государственный комитет

Совете Министров СССР оо делам,, иэеоретений и открытий (53) УДК 621.373.072.9 (088.8) (72) Авторы изобретения Г. А. Иванов, H. И. Оспищева, В. И. Кардаш и А. Я. Костинский (71) Заявитель (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ

Изобретение относится к импульсной технике.

Известно устройство синхронизации, содержащее генератор, управляемый напряжением, делитель, запрограммированный делитель, состоящий из триггеров, логические элементы

И, ключи, детекторы превышения импульсов, генератор стандартных сигналов, декадный счетчик и формирователь с инвертором (1).

Данное устройство имеет сложную схему.

Наиболее близко к предлагаемому устройство синхронизации, содержащее выходной логический элемент И, один из входов которого соединен с выходом триггера, а другой — с выходом формирователя, вход которого соединен с шиной синхронизации, два дополнительных триггера, один из входов каждого из которых подключен к выходувыходного логического элемента И, а другой— к шине «сброс», и два логических элемента

И, выходы которых подключены к соответствующим входам первого из упомянутых триггеров, одни из входов каждого из которых через инвертор соединены с выходом формирователя, а другие подключены соответственно к выходам второго и третьего триггеров (2).

Данное устройство не позволяет получить выходные импульсы с длительностью, равной длительности синхросигналов.

Цель изобретения — формирование выходного сигнала с длительностью, равной длительности синхросигнала — достигается тем, что в устройство синхронизации, содержащее

5 выходной логический элемент И, один из входов которого соединен с выходом триггера, а другой — с выходом формирователя, вход которого соединен с шиной синхронизации, два дополнительных триггера, один из

10 входов каждого из которых подключен к выходу выходного логического элемента И, а другой — к шине «сброс», и два логических элемента И, выходы которых подключены к соответствующим входам первого из упомя15 нутых триггеров, одни из входов каждого из которых через инвертор соединены с выходом формирователя, а другие подключены соответственно к выходам второго и третьего триггеров, введены два дополнительных логи20 ческих элемента И, выходы которых соединены с третьими входами второго и третьего триггеров, один из входов каждого дополнительного логического элемента И соединен с выходом формирователя, второй вход одного

25 из дополнительных логических элементов И соединен с выходом первого триггера, а второй .вход другого дополнительного логического элемента И подключен к шине «установка», при этом третий вход первого триггера

3;) подключен к шине «Сброс».

553737

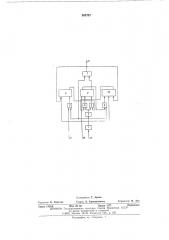

Структурная электрическая схема описываемого устройства приведена на чертеже.

Устройство содержит формирователь 1, ин вертор 2, логические элементы И 3 — 7, триггеры 8 — 10. На шину 11 подается сигнал

«Установка», на шину 12 — сигнал «Сброс», а на шину 13 — сигнал синхронизации. Выходной сигнал снимается с выхода 14. Источники сигналов на схеме не показаны.

Принцип работы устройства заключается в следующем.

В исходное состояние устройство синхронизации переводится сигналом, поступающим по шине «Сброс» 12. При наличии признака запуска, поступающего на шину 11, и внешнего синхроимпульса, поступающего по шине

13 в фо|рмирователь 1, на выходе элемента

И 3 формируется сигнал, устанавливающий триггер 8 в единичное состояние. Если триггер 8 не успевает установиться в единицу по данному синхроимпульсу, устройство запускается следующим синхроимпульсом.

По единичному состоянию триггера 8 при отсутствии внешнего синхроимпульса на выходе элемента И 5 формируется сигнал, устанавливающий триггер 9 в единичное состояние. Признаком отсутствия входного синхроимпульса является разрешающий потенциал на выходе инвертора 2. При наличии внешнего синхроимпульс инвертор 2 формирует потенциал запрета сигнала установки в единицу триггера 9. Синхроимпульс, поступающий в устройство вслед за запускающим, опрашивает единичное состояние триггера 9, в результате чего элемент И 7 вырабатывает сигнал, синхронизированный с внешними синхроимпульсами. Этот же сигнал устанавливает в единичное состояние триггер 10. Если сигнал запуска устройства не сброшен, он сбрасывается этим же сигналом.

После окончания очередного синхроимпульса по единичному состоянию триггера 10 и разрешающему потенциалу с выхода инвертора 2 на выходе элемента «И» 4 формируется сигнал, сбрасывающий триггер 9, По нулевому состоянию триггера 9 и очередному внешнему синхроимпульсу на элементе И 6 формируется сигнал, сбрасывающий триггер

10, после чего устройство переводится в исходное состояние.

Устройство позволяет синхронизировать сигналы между внешними устройствами с

5 различными системами элементов (например, импуль сно-потенциальной и потенциальной) без дополнительного формирования сигнала по длительности. Использование одной серии синхроимпульсов позволяет обойтись

10 без дополнительного генератора.

Формула изобретения

Устройство синхронизации, содержащее выходной логический элемент «И», один из

15 входов которого соединен с выходом триггера, а другой — с выходом формирователя, вход которого соединен с шиной синхронизации, два дополнительных триггера, один из входов каждого из которых подключен к выходу

20 выходного логического элемента И, а другой подключен к шине «сброс», и два логических элемента И, выходы которых подключены к соответствующим входам первого из упомянутых триггеров, одни из входов каждого из

25 которых через инвертор соединены с выходом формирователя, а другие подключены соответственно к выходам второго и третьего триггеров, отличающееся тем, что, с целью формирования выходного сигнала с

ЗО длительностью, равной длительности синхросигнала, в него введены два дополнительных логических элемента И, выходы которых соединсны с третьими входами второго и третьего триггеров, один из входов каждого до35 полнительного логического элемента И соединен с выходом формирователя, второй вход одного из дополнительных логических элементов И соединен с выходом первого триггера, а второй вход другого дополнительного ло40 гического элемента И подключен к шине

«Установка», при этом третий вход первого триггера подключен к шине «Сброс».

Источники информации, принятые во внимание при экспертизе:

45 1. Патен" США М 3813610, кл. 331-1А, 28. 05.74.

2. Патент США Хо 3504200, кл, 307-269, 21.06.70.

553737

Составитель T. Артюх

Техред А. Камышникова

Редактор Б. Федотов

Корректор Н Аук

Заказ 1101/6 Изд. Ио 32 Тираж 1077 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобре-ений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, р