Устройство для выделения из двух функций экстремальной

Иллюстрации

Показать всеРеферат

Х йк"чт е

ОЛ ИС

ИЗОБРЕТЕНИЯ (») 555397

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22} Заявлено 21.04.75 (21) 2126252/24 с присоединением заявки № (51) М. Кл.е

G06 F 7/02

Гасударственный комитет

Совета Министров СССР во делам изаоретений н открытий (23) Приоритет (53) УДК 681.325 (088.8) (43) Опубликовано 25.04,77. Бюллетень № 15 (45) Дата опубликования описания 28,06.77 (72) Авторы изобретения

В. Д. Самойлов, А. А. Баньва и Н. Л. Никонова

Институт электродинамики АН Украинской CCP (7е) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ИЗ ДВУХ ФУНКЦИЙ

ЭКСТРЕМАЛЬНОЙ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств аналогоцифровых вычислительных систем.

Известны устройства для выделения экстре- 5 мальной из двух сравниваемых функций, в состав которых входят схемы сравнения кодовых сигналов или схемы сравнения кодов (12 и (22. Эти устройства определяют максимальную или минимальную величину из двух сравниваемых в случае, если известны их полноразрядные коды, что влечет за собой значительные затраты оборудования, возрастающие по мере увеличения разрядности сравниваемых величин.

Наиболее близким к изобретению является устройство для выделения экстремальной из двух функций, содержащее входной сумматор, один из входов которого соединен с первой входной шиной, а второй — через первый инвертор с второй входной шиной, выход сумматора подключен к входу 20 двоичного счетчика, выходной сумматор, . узел управления, интегратор, элементы И, ИЛИ, инверторы (32. !

Это устройство не дает возможности сравнивать непрерывно изменяющиеся величины, а производит выделение экстремальной из двух сравниваемых величин в случае, если известны их полноразрядные коды, что приводит к излишним затратам оборудования.

Целью настоящего изобретения является упрощение устройства.

Достигается это тем, что в устройстве выход переполнения двоичного счетчика соединен с вхо. дами первого и второго элементов И, друтие входы которых подключены к выходам узда управления, а их выходы соединены с одним из входов элемента

ИЛИ н с входом второго инвертора соответственно, выход второго инвертора подключен к другому входу элемента ИЛИ, выход которого соединен с одним из входов третьего элемента И и через третий инвертор — с одним из входов четвертого элемента

И, другой вход которого соединен с первой входной шиной, а выход подключен к одному из входов выходного сумматора, выход которого подключен к входу интегратора, а другой вход — к выходу третьего элемента И, другой вход которого соединен с второй входной шиной.

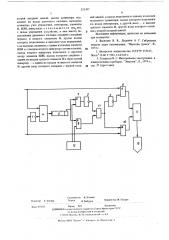

На чертеже изображено предлагаемое устройство.

Предлагаемое устройство содержит инверторы

1 — 3, сумматоры 4 и 5, двоичный счетчик 6, 555397 I%«a . Я х (О) 10) $ (о) (о) (o) У = -,(х, х, /» /3

L-GIiIH !! или величина (a) (т) О) дх =ах -дхг

Х х +Ах

),и)1и Х. - 0

5I f II l

-),пр1 Х 0 элементы И 7 — 10, элемент И31И 11, узел управления 12, интегратор 13.

Устройство работает следующим образом.

П ред началом решения в двоичный счетчик 6 ер

Ia) >(о) Lo) заносится начальное знач.ние величины Хз=х, — х, где хl) — начальное полноразрядное значение первой из сравниваемых величин; х — начальное полноразрядное значение втор ой

2 иэ сравниваемых величин, а индекс в круглых скобках указывает номер шага сравнения.

В цифровой интегратор 13 заносится начальное (о) значение выходной величины у, равное что представляет собой значение минимальнои величины в начальный момент времени в случае выделения минимальной величины, либо равное в случае выделения максимальной величины.

Далее с выхода узла управления на вход элемента И 7 поступает потенциал, разрешающий прохождение сигнала с выхода двоичного счетчика на вход элемента ИЛИ 11.

На первом шаге сравнения на,вход сумматора 4 и на вход элемента И 9 поступает одноразрядное приращение Лх, одной иэ сравниваемых величин, а и) на вход инвертора 1 и на вход элемента И 10— и) одноразрядное приращение 6х> второи из сравниваемых величин. На выхоце инвертора 1 форми(а) руется сигнал, равный Ьх,, а на выходе сумматора

4 сигнал

Сигнал Ьхэ поступает на вход двоичного счетчика 6, в котором образуется значение переменной хэ на первом шаге сравнения, равное (О

Выходной сигнал знакового разряда счетчика поступает на вход элемента И 7 (в случае выделения минимальной величины), либо на вход элемента И 8, (в случае выделения максимальной величины).

Сигнал с выхода двоичного счетчика 6 может быть описан следующей зависимостью

).-61Д)1 Х э О, rip)I х э>0

2 1,rlð)1 )i. сО, где xi — число, зашгсашгос в эиа Il!LLLIIX. раэря,рх счетчика 6, а

На выходе инвертора 2 (в случае выделения ьи.нимальной величины) образуется сигнал, равныи

Таким образом, на выходе элемента ИГПИ

Ипи появляется сигнал, равный в случае выделения минимальной величины, либо равный в случае выделения максимальной величины. На выходе сумматора 5 формируется величина

И (4)

fd и) 1-8Яихз (!I 1 1 и ду =Ьх, 2 з +дх

И и) и) и) и) 4+&фпЪэ 1)) k-64)) "э

1 Ь <дХ в случае вьщеления максимальной величины.

Сигнал с выхода сумматора 5 поступает на вход интегратора 13, в котором происходит образование величины у =у +Лф), представляющей собой минимальное либо максимальное из двух сравниваемых чисел на данном шаге (в зависимости от состояния узла управления) .

На следующем такте сравнения на входы схемы поступают одноразрядные приращения сравниваемых величин Ьх, и Ьх, и описанный выше путь прохождения входных сигналов в предлагаемом устройствЕ повторяется.

4О Таким образом, иа любом К-он шаге сравнения в инте).раторе 13 будет сформирована величина, равная максимальной или минимальной величине из двух сравниваемых в данный момент времени (в зависимости or состоянии узна сравнения) .

4> Использование рассмотренного выше устройства дает возможность сравнивать непрерывно изменяющиеся величины, причем в момент сравнения ие требуется знать их полноразрядные коды, что приводит к сокращению оборудования в устройстве, так как не требуются рег)1стры или другие узлы для запоминания этих иолноразрядных кодов. Все это приводит к упрощению устройства.

Формула изобретения

Ус)ройство )ц)я вьшслсиия иэ двух функций эксгрсмгс)ыгой, содержащее 11хо;и;Ой сул)матор, OiLI1l1 ИЗ ВХОЛОВ КО1ОРОГО Coi. !IIIII!. II С III. f>!IOII ВХОД

Q) иой IIIIIII(IIi, а дтГ>рой — чсрсэ исриый 11111ср)ор — i;o

555397

Гооааант иь В, Белкин

Е Бабурка

Корректор И. Гоксич

Ролактор 1:. Гончар

Тираж 818 По ингоноо!

1!1!!ИПИ Гогу.!арф гианного комита га (.аиста Миниотрои (.С(. Р но ионам ttçîáðåòt íèé и о крытнП

113!!3(. Моокна, Ж-35. аунккаи наб., л, 4,, 5

:3акаа 459/33

Я>иона:t 1нтг! "1!атонт". и. Ужгороч, уи. Г1роск и:ик 4 второй входной шиной, выход сумматора подключен ко входу двоичного счетчика, выходной сумматор, узел управления, интегратор, элементы

И, ИЛИ, инверторы, о т л и ча ю ще е ся тем, что, с целью упрощения уст! ойства, в нем выход переполнения двоичного счетчика соединен с входами первого и второго элементов И, друтие входы которых подключены к выходам узла управления, а их выходы соединены с одним из входов элемента

ИЛИ и с входом второго инвертора соответственно, выход второго инвертора подключен к другому входу элемента ИЛИ, выход которого соединен с одним из входов третьего элемента И и через третий инвертор — с одним из входов четвертого элемента

И, другой вход которого соединен с первой входной шиной, а выход подключен к одному из входов выходного сумматора, выход которого подключен ко входу интегратора, а другой вход — к выходу третьего элемента И, другой вход которого соединен с второй входной шиной.

Источники информации, принятые во внимание при экспертизе:

1. Васильев В. В., Додонов А. Г. Гибридные модели задач оптимизации, "Наукова думка", К., !

О 1973 r.

2. Авторское свидетельство СССР У 355615, М.кл. G 06 F 7/02, 12.03.69 r.

3. Гутников В. С. Интегральная электроника в измерительных приборах, "Энергия", Л., 1974 г..

15 стр. 37. (прот тип).