Матричное вычислительное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 09.06.75. (21) 2142322/24 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.04.77. бюллетень № 15 (45) Дата опубликования описания28.06,77

Союз Советских

Социалистических

Республик (51) М. Кл.

G 06 F 7/38

Гасударственный камнтет

Савата Мнннстраа СССР аа делам нэааретеннй н аткрытнй (53) УДК 681 325 5 (088.8) (72) Авторы изобретения

Е. И. Брюхович и А. M Карцев (71) Заявитель

Ордена Ленина институт кибернетики АН Украинской ССР (54) МАТРИЧНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах, работающих как в позиционных системах счисления, так и в непозиционных системах остаточных классов. 5

Известно устройство для выполнения арифметических и логических операций. Это устройство содержит прямоугольную матрицу из логических ячеек и управляющих ячеек — по одной на каждом из столбцов матрицы. Каждая управляющая ячейка 1о состоит из двух каскадов, может находиться в состоянии "1" либо "0" и служит для управления всеми операциями, выполняемыми соответствующим столбцом. Каждая ячейка матрицы, также состоящая из двух каскадов, связана с соответствующей управляющей ячейкой и вырабатывает выходные сигналы в зависимости от трех входных сигналов. Каждый столбец матрицы может быть выбран с целью выполнения соответствующей . арифметической или логической операции. 20

Известно также устройство, которое иредназна. чено для сложения, вычитания, умножения, деления, возведения в степень, извлечения корня и перекодирования многоразрядных двоичных чисел.

Устройство содержит блоки сложения и вычи- 25 тания с шунтирующим управлением. Каждый блох имеет два входа операндов, вход переноса (занятия единицы из десятка прн вычитании), а также выход суммы илн разности.

Все эти устройства выполняют ограниченный набор операций. Кроме того, они не позволяют строить вычислительные машины, которые могут работать как в позиционной системе счисления, так н в инерционной системе счисления остаточныХ классов.

Наиболее близким к изобретению по своей технической сущности является матричное вычис. лительиое устройство, содержащее блоки расстанов. кн операндов и сравнения операндов, входы ко. торых подключены к двум входам устройства, и матрицу памяти. Это устройство имеет большое количество аппаратуры, что вызывает большие затраты, значительную часть которых составляет матрица памяти, содержащая Р(Р-1) / Й двухвходовых элементов И при основании системы счисления P.

Целью изобретения является сокращение оборудования устройства.

Достигается это тем, что устройство содержит блоки распознавания, коммутации, формирования

555400

1 и равляняцих сигнал<) в, вторичной расстановк. операндов и определения совпадения входных сигналов, причем вход первого блока расноз)гавания подключен к выходу блска расстановки операндов, первый и второй входы первого блока коммутации подключены соответственно к выходам блока расстановки операндов и первого блока распознавания, входы второго и третьего блоков распознавания подключены соответственно к первому и второму выходам первого блока коммутации, первый и второй входы второго блока коммутации соединены соответственно с первым выходом пер. вого блока коммутации и первым выходом блока формирования управляющих сигналов, входы которого соединены соответственно с выходами второго и третьего блоков распознавания, первые входы блока вторичной расстановки операндов и блока определения совпадения входных сигналов соединены с вторым выходом первого блока коммутации, вторые входы — с выходом второго блока коммутации; выход блока вторичной расстановки операндов через матрицу памяти соединен с первым входом третьего блока коммутации, второй и третий входы которого подключены соответственно к выходу блока определения совпадения входных сигналов и к второму выходу блока формирования управляющих сигналов, первый и второй входы четвертого блока коммутации подключены соответственно к выходам третьего блока коммутации и первого блска распознавания, выходы четвертого блока коммутации и блока сравнения операндов соединены с соответствующими выходами устройства.

Блоки распознавания и блок формирования управляющих сигналов вырабатывают управляющие сигнал»! в зависимости от того, к какой из частей таблицы, отобража>мой матрицей памяти, осуществляется обращение; блоки коммутации необходимы для подклв)чения входов и выходов матрицы памяти к входам и выходам матричного вычислительного устройства соо)встственно по сигналал., вырабатываемым блоками распознавания и блоком формирования управляющих си ))a!)os; блок вторичной расстановки операндов и блок совпадения входных сигналов необходимы для исключения избыло нных элементов матрицы памяти. Это позволяет использовать каждьш двухвходовый элемент И матрицы памяти для определения группы и общем случае разтшчных значений.

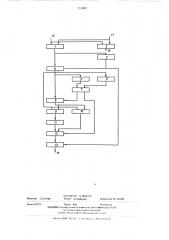

На чертеже представлена блок-схема матричного вычислите.ibso! o устройства.

Прел))агасмая блок-схема содержит блок 1 расстановки операндов, блок 2 сравнения операндов, блок 3 раси< з)гавания. блок 4 коммутации, блоки 5, 6 распознавания. блок 7 формирования управляющих сг)палов, блок 8 комл)ута)гии, блок 9 вторичной расстановки операндов, блок 10 определения совпадения входных сигналов, матрица 11 памяти, блоки 1 и 13 кол)л)угации, выходы 14, 15

H входы 16, 1 7 уcTpo)IcI Bs.

Блок 3 имеет число входов, равное выбранному основанию системы счисления, и реализуется с помощью элементов И, ИЛИ.

Блок 4 представляет собой матрицу элементов

5 И и содержит число вертикальных шин, равное выбранному основанию, и две горизонтальные шины. Входы элементов И, расположенных в однои строке (в одном столбце), подключены соответственно к одной горизонтальной (вертикальнои

10 шине). Блоки 5, 7 реализуются с использованием элементов И, ИЛИ. Блок Ь представляет собой многовходовую схему ИЛИ. Блок 8 представляет собой матрицу элементов И, горизонтальные шины которой подключены соответственно к выходам

16 блока 7, а вертикальными шинами блока 8 являются те же выходы блока 4, которые являются входными для блока 5.

Блок 9 представляет собой набор двухвходовых элементов ИЛИ, блок 10 — набор двухвходоЮ вых элементов И.

Блок 12 представляет собой матрицу элементов

И, вертикальные шины которой подсоединены к выходам матрицы 11 и блока 10, а горизонтальные шины подсоединены соответственно к выходам

25 блока 7.

Блок 13 представляет собой матрицу элементов

И, вертикальные шины которой подсоединены к выходам блока 12, а горизонтальные — к выходам блока 3.

80 Матричное вычислительное устройство работает следующим образом, Операнды с входов 16, 17 устройства поступают на входы блоков 1 и 2. Если операнды равны, то сигнал поступает на выход 15 устройства по выходу блока 2, номер которого равен величине любого из операндов.

Если операнды не равны, то в блоке 1 возбуждаются два выхода, номера которых совпадают с величинами операндов соответственно. Сигналы посту)!а!от на входы блоков 3, 4. В блоке 3 вырабатывается управлягощий сигнал на одном из выходов, в блоке 4 осуществляется передача каждого из двух сигналов, к одному из двух выходов, в зависимости от того, на какой из управляющих входов поступае г сипгал от блока 3.

Д))я четных (нечетных1 з))ачсни)1 основания с выходов блока 4 сигналы, соответствующие оllерандам, поступают на одноименные входы блоков

5, 8 или иа соогвстству)ощис входы блоков 6, 9, 10.

Г выходов блоков S и 6 сигна)п» поступают на вход блока 7, который вырабиываст управляющие сигналы на соответствующих выходах.

В блоке 8 осуществляется передача сигналов, поступан)щих от т)н)б)ого из выхолив блока 4 к о)шому из двух выходов. в зависимости oi того, на какой из управляющих входов ))ос)упа I сигнал из блока 7.

С выходов блока 8 сигналь! посгупают )>а соотвстствуюнпгс входы блоков 9 и 10.

Выходи! )с с!т! нач),! б)))!)ка 9:!ос>у;)а)ol !!s Bxojlbl

6О л)>)т!)))ць! 1 1, )! ыхд ss>1ñ сиг)>а)))>! коГ(э!)ой >! б )ока 10

555400 поступают на вход блока 12. Одновременно по одному из управляющих входов блока 12 поступает сигнал с выхода блока 7. С выхода блока 12 сигнал поступает на вход блока 3.

Одновременно по одному из управляющих входов блока 13 поступает сигнал с соответствующего выхода блока 3. При этом, на выходе блока 13 появляется сигнал, соответствующий результату операции, Минимальный положительный эффект от внедрения изобретения по сравнению с известным устройством наблюдается при основании большем 30. Экономический эффект от внедрения устройства тем больше, чем больше величина основания.

Формула изобретения

Матричное вычислительное устройство, содержащее блоки расстановки операндов и сравнения операндов, входы которых подключены к двух входам устройства, и матрицу памяти, о т л и ч а ющ е е с я тем, что, с целью сокращения оборудования, оно содержит блоки распознавания, коммутации, формирования управляющих сигналов, вторич- ной расстановки операндов и определения совпадения входных сигналов, причем вход первого блока распознавания подключен к выходу блока расстановки операндов, первый и второй входьь первого блока коммутации подключены соопзетственно к выходам блока расстановки операндов и первого блока распознавания, входы второго и третьего блоков распознавания подключены соот6 ветственно к первому и второму выходам первого блока коммутации, первый и второй входы второго блока коммутации соединены соответственно с первым выходом первого блока коммутации и 0 первым выходом блока формирования управляющих сигналов, входы которого соединены соответственно с выходами второго и третьего блоков распознавания, первые входы вторичной расстановки операндов и блока определения совпадения входных сигналов соединены с вторым выходом

l6 первого блока коммутации, вторые входы — с выходом второго блока коммутации, выход блока вторичной расстановки операндов через матрицу памяти соединен с первым входом третьего блока коммутации, второй и третий входы которого

20 подключены соответственно к выходу блока определения совпадения входных сигналов и к второму выходу блока формирования управляющих сигналов первый и второй входы четвертого блока

l коммутации подключены соответственно к вы36 ходам третьего блока коммутации и первого блока распознавания, выходы четвертого блока коммутации и блока сравнения операндов соединены с соответствующими выходами устройства.

555400!

Составитель А- Жеренои

Техрел Н. Бабурка

В.лактор E. Гончар

Корректор И. Гоксич

Заказ 459/23

<Ь глинн llllll (4 еи ", г. Ужг ори I. s:I. (ll к к)нам. 4

Тираж 8! 8 Полниснос

llHHHIlH I îñóцарсгиенного комнгс а (овеса \|инисгров (((Р

llo ленам изобретений и î I êðü> I èé

l 13035. Москва, Ж-35. Раъ!пекин най., л, 4/5