Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

О П И С А Н И Е („ 555438

ИЗОБРЕТЕH ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заивлено 01,09.75(21) 2167345/24 с присоединением заявки № (23) Приоритет— (43) Опубликовано 25.04.77Бюллетень № 15 (45) Дата опубликования описания 17.05.77 (51) М. Кл.е

5 11 С 15/00

Государственный комитет

Совета Министров СССР по делам иэооретений н открытий (53) УДК 681.327.6 (088.8 ) (72) Автор изобретения

Б. В. Барашенков (71) Заявитель (54) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство для определения достоверности и контроля в процессе функционирования хранящейся информации, в котором используется метод схемного и информационного дублирования запоминающей матрицы устройства (lf.

Структурно это решается с помощью связей выходов индикаторов и шин считы- 1О вания запоминающих матриц с элементами сравнения, что позволяет осуществлять

"пословную" обработку информации (сравнение считываемых слов и результатов поиска в двух ассоциативных матрицах между 15 собой). Это приводит к значительной информационной и схемной избыточности этого устройства.

Из известных устройств наиболее близким техническим решением к изобретению является ассоциативное запоминающее устройство, содержащее блок управления, подключенный к блоку сравнения, элемент И и управляющие шины P2).

Недостатком этого устройства является большая информационная и схемная избыточность ассоциативной памяти, состоящая в необходимости использования второй (дублирующей) матрицы ассоциативной памяти.

Целью изобретения является упрощение устр ойства.

11остигается это тем, что устройство содержит сумматоры по модулю два, коммутатор и дополнительный блок сравнения, входы первого и второго сумматоров по модулю два подключены к соответствующим выходам блока памяти, выход первого сумматора по модулю два соединен с входом коммутатора, выходы которого подключены к одним входам дополнительного блока сравнения, другие входы которого соединены с выходами третьего сумматора по модулю два, выходы второго сумматора по модулю два и блока сравнения подключены соответственно к входам элемента И и третьет о сумматора по модулю два; входы блока сравнения подключены к управляющим шинам и одному из выходов блока управления, другие выходы которого соединены с

555438

Перед началом работы устройства в составе ЭВМ сигналами от блока управления 8 производится запись "0" во все ячейки блока памяти 1, а также сброс в состояние "0 сумматоров 3 и 4 по модулю два. При заполнении блока памяти 1 информацией производится обращение к устройству с поиском нулевого слова (приэнак поиск и код числа 0 на уп- 45 равляющих шинах 12 и 10 соответственно), которое считывается на управляющую шину 11 с некоторого адреса блока памяти 1 с последующей записью кода числа от ЭВМ по этому адресу. 50

Этот процесс записи сопровождается определением контрольной суммы информации, записываемой в устройство. Происходит это следующим образом. Коды чисел от ЭВМ, записываемые в блок памяти 1, 55 поразрядно сравниваются с помощью блока сравнения 7 с содержанием тех ячеек блока памяти 1, в которые производят запись, В процессе сравнения на выходах соответствующих разрядов блока сравнения 7 50 входами второго и третьего сумматоров по модулю два, элемента И и коммутатора.

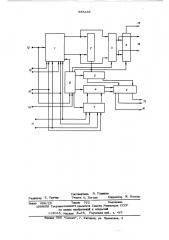

На чертеже дана блок-схема устройства.

Ассоциативное запоминающее устройство содержит блок памяти 1, первый, второй и третий сумматоры 2, 3, 4 по модулю два, коммутатор 5, дополнительный блок сравнения 6, блок сравнения 7, блок управления

8, элемент И 9, управляющие шины 10-14, выходные шины 15-18. 10

Входы первого 2 и второго 3 сумматоров по модулю два подключены к соответствующим выходам блока памяти 1, выход первого сумматора 2 по модулю два соединен с входом коммутатора 5, выходы которого 15 подключены к одним входам дополнительного блока сравнения 6, другие входы которого соединены с выходами третьего сумматора 4 по модулю два, выходы второго сумматора 3 по модулю два и блока сравнения 7 подключены соответственно к входам элемента И- 9 и третьего сумматора 4 по модулю два, входы блока сравнения 7 подключены к управляющим шинам 10 и 11 и одному из выходов блока управления 8, 25 другие выходы которого соединены с входами второго 3 и третьего 4 сумматоров по модулю два элемента И 9 и коммутатора 5.

Устройство работает в двух режимах. 30

Первый режим — определение контрольной суммы информации, записываемой в устройство, и второй - определение контрольной суммы информации, хранящейся в устройстве. 35

4 появляются сигналы "1 (случае несовпадения) и "0" (в случае совпадения), поступающие на соответствующие входы сумматора 4 по модулю два, где происходит их сложение с предыдущим значением результата суммы и запоминание в сумматоре 4 по модулю два.

В результате начального заполнения информацией блока памяти 1 в сумматоре

4 по модулю два накапливается поразрядная сумма по модулю два всех слоев, записываемых в блок памяти 1, так как начальное содержание блока памяти составляли "нулевые слова.

В дальнейшем при записи (приэнак "Запись — на управляющей шине 12) кодов чисел от ЭВМ в ячейки с произвольным содержанием меняются на противоположные значения те разряды контрольной суммы, хранящейся в сумматоре 4 по модулю два, которые не совпадают у считываемого и записываемого кодов чисел. При этом предполагается, что операции записи всегда предшествуют считыванию с некоторого адреса блока памяти, в который должна производиться запись. При начальном заполнении устройства считывание может не производиться, так как начальное содержащие блока памяти 1-"нулевое". При считывании информации сигналами от блока управления 8 производится запрет передачи информации от блока сравнения 7 в сумматор 4 по модулю два

Для контроля хранящейся в блоке памяти 1 информации блок управления 8 по си1 калу "Контроль", поступающему о ЭВМ по управляющей шине 14, запрещает поступление информации в сумматор 4 по модулю два от блока сравнения 7. Одновременно с сигналом "Контроль" от ЭВМ поступают ситналы "Поиск по управляющей шине 12 и "1 " - по управляющей шине 10, последовательно по каждому из разрядов устройства, причем все остальные разряды маскируются кодом маски по управляющей шине 13. Тем самым на выходах индикаторов совпадения блока памяти 1 последовательно фиксируется информация, хранящаяся во всех ячейках разряда, по которому производится поиск "1" .

Сумматор 2 по модулю два образует значение "вертикальной" суммы по мощ» лю два информационного содержания разряда всех слоев блока памяти 1, которая с помощью коммутатора 5 сравнивается с соответствующим значением разряда контрольной суммы, хранящейся в сумматоре 4 по модулю два с помощью дополнительного блока сравнения 6, 555438

Ассоциативное запоминающее устройство, содержащее блок управления, подключенный к блоку памяти и блоку сравнения, элемент И и управляющие шины, о т л и ч а ю щ е е с я тем, что, с цепью упрощения устройства, оно содержит сумматоры по модулю два, коммутатор и дополнительный блок сравнения, входы первого и второго сумматоров по модулю два подключены к соответствующим выходам блока памяти, выход первого сумматора по модулю два соединен с входом коммутатора, выходы которого подключены к одним входам дополнительного блока сравнения, другие входы которого соединены с выходами третьего сумматора по модулю два, выходы второго сумматора по модулю два и блока сравнения подключены соответственно к входам элемента И и третьего сумматора по модулю два, входы блока сравнения подключены к управляющим шинам и одному из выходов блока управления, другие выходы которого соединены с входами второго и третьего сумматоров по модулю два, элемента И и коммутатора.

Источники информации, принятые во внимание при экспертизе:

1, Патент Великобритании ¹ 1265013, М. кл. 611 С 15/00, 1972 г.

2. Патент Великобритании ¹ 1265014, М. кл. 5 11 С 15/00, 1972 (проготип) .

При окончании цикла поиска " < " по всем систему ортогональных проверок на четразрядам дополнительным блоком сравне- ность, с помощью которых могут быть ния 6 при несовпадении контрольной суммы указаны как адрес, так и разряд ошибки. записанной и хранящейся в устройстве информации на шине 16, вырабатывается сигнал "Ошибка" и код результата сравнения Формула изобретения на шине 17. Параллельно с образованием

"вертикальной" суммы, в процессе пораз= рядного ассоциативного поиска происходит образование горизонтальной" суммы по мо- щ дулю два информационного содержания каждого слова.

Это происходит следующим образом.

По сигналу Контроль" блока управления

8 информация c BbIxDgG каждого индикатора совпадения блока памяти 1 поступает на соответствующие входы сумматора 3 по модулю два, который производит суммирование информации по модулю два с запоминанием результата. 20

Предполагается, что один разряд блока памяти является контрольным и дополняет до сумму по модулю два информационных разрядов. Затем производится опрос состояния сумматора 3 по модулю два. В 25 том случае, если на всех выходах сумматоров 3 оказывается сигнал "1", элемент

И 9 образует сигнал отсутствия ошибки.

В противном случае, при нечетном количестве ошибок в каком-либо слове на ши- 30 нах 18 и 15 образуется сигнал "0", сит нал ошибки и код результата суммированияна шинах 18 с указанием адреса ошибки памяти 1.

Рассмотренные циклы контроля можно З5 периодически использовать в качестве теста проверки хранения информации устройства, либо после каждой операции "запись"для проверки правильности занесения информации в устройство. 40

Таким образом, проверки на четность— вертикальные и горизонтальные — образуют

555438

Составитель B. Рудаков

Техред А. Богдан Корректор Ж. Кеспер

Редактор Е. Гончар

Сапаап ППП "Патент, r. Ужгород, ул. Проектная, 4

Заказ 466/25 Тираж 762 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР о делам изобретений и открытий

113О35, Москва Ж35, Раушская наб., д. 4/5