Интегрирующее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ (i i) 556455

Союз Советских

Сощиалистимеских

Респубпик (61) Дополнительное к авт. свид-ву (22) Заявлено 03,04.75 (21) 2120249/24 с присоединением заявки № (23) Приоритет

Опубликовано 30.04.77. Бюллетень № 16

Дата опубликования описания 31.05.77 (51) М. Кл,2 G 06G 7/18

Гооударстеенный комитет

Соеета Мнннстеое СССР пе делам изооретений н открытий (53) УДК 681.335(088.8) (72) Авторы изобретения

А. Ю. Дворниченко, Ц. И. Вайсберг и И. И. Лозиева (71) Заявитель (54) ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может быть использовано в аналоговых вычислительных машинах, в устройствах автоматики и измерительной техники.

Известно устройство для интегрирования, состоящее из операционного усилителя с емкостной отрицательной обратной связью и генератора тактовых импульсов (1). Погрешность интегрирования такого устройства зависит от соблюдения условия

t« (1+А) RC, где — величина времени интегрирования;

А — коэффициент усиления операционного усилителя;

RC — интегрирующая цепочка интегратора.

В современных операционных усилителях коэффициент усиления составляет 5 — 10 тыс, Увеличение времени интегрирования, при сохранении неизменными А и ЯС ведет к увеличению погрешности интегрирования до 1% и более в зависимости от величины времени интегрирования.

Известно интегрирующее устройство, содержащее интегратор с обнулением, подключенный к первому входу сумматора, запоминающий блок и генератор тактовых импульсов (2).

Выходное напряжение интегрирующего устройства получается суммированием отдельных участков пилообразного напряжения.

Время интегрирования и точность интегрирования известного интегратора зависят от ве5 личины порогового напряжения блока сравнения. При интегрировании входных сигналов, имеющих разную скорость изменения, для обеспечения необходимой точности интегриро-. вания необходимо изменять пороговое напря10 жение. В реальных интегрирующих устройствах порог срабатывания устанавливают некоторой средней величины, что приводит к снижению точности интегрирования медленно меняющихся сигналов.

15 Целью изобретения является повышение точности интегрирования.

Поставленная цель достигается тем, что выход сумматора подключен к входу запоминающего элемента, выход которого соединен с

20 вторым входом сумматора, а управляющий вход запоминающего элемента связан с генератором тактовых импульсов, соединенным через введенный -элемент задержки с входом сброса интегратора с обнулением.

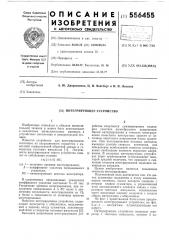

25 На фиг. 1 представлена блок-схема предложенного интегрирующего устройства; на фиг.

2, а — е — диаграммы, иллюстрирующие его работу.

Интегрирующее устройство содержит гене30 ратор 1 тактовых импульсов, элемент 2 за556455 держки, интегратор 3 с обнуленисм, запоминающий блок 4 и сумматор 5. Выход сумматора является выходом устройства.

Рассмотрим работу интегрирующего устройства, начиная с момента времени 11 для случая поступления на его вход сигнала в виде постоянного напряжения (фиг. 2). Поступившее на вход интегратора 3 с обнулением постоянное напряжение (фиг. 2, а) интегрируется и подается на сумматор 5. На интервале времени t1 — t> выходное напряжение сумматора 5 повторяет форму напряжения интегратора 3 с обнулением, так как при этом напряжение на запоминающем блоке 4 равно 0 (фиг. 2,г, д, е). В момент времени 4 на запоминающий блок 4 поступает импульс с генератора 1 тактовых импульсов (фиг. 2,б), и запоминающий блок 4 фиксирует напряжение, поступающее с выхода сумматора 5 (фиг. 2, д, е).

В момент 4 зафиксированное напряжение с выхода запоминающего блока 4 поступает на сумматор 5 и в этот же момент интегратор 3 с обнулением обнуляется (фиг. 2,г). Обнуление интегратора 3 осуществляется импульсами, поступающими с элемента задержки 2 (фиг. 2, в). Напряжение запоминающего блока 4 поступает на вход сумматора 5, на другой вход которого подано напряжение интегратора 3 с обнулением. Обнуление интегратора 3 происходит в момент времени 4 (фиг.

2, в), т. е. после того, как произведена фикса ция напряжения cyììàòîðà 5.

Работа устройства на интервале времени

tç — 4 — 4 происходит аналогично. При этом на сумматоре 5 осуществляется суммирование напряжения интегратора 3 с обнулением и

cT) ï1. í 13òoÃo напряжени11 запомнн<1к)1цего блока 4. Величина ступенчатого напряжеши запоминающего блока равна значению напряжения сумматора в предыдущий такт. Полу5 ченное на сумматоре 5 пилообразное напряжение (фиг. 2,д) имеет погрешность интегрирования 0,01 /О на всем интервале интегрирования входного сигнала.

Высокая линейность выходного напряжения

10 на всем временном интервале обусловлена тем, что выходное напряжение интегрирующего устройства получается суммированием отдельных участков пилообразного напряжения с высокой линейностью.

Формула изобретения

Интегрирующее устройство, содержащее интегратор с обнулением, подключенный к первому входу сумматора, запоминающий блок

20 и генератор тактовых импульсов, о т л и ч а ющ е е с я тем, что, с целью повышения точности интегрирования, выход сумматора подключен к входу запоминающего элемента, выход которого соединен с вторым входом сум25 матора, а управляющий вход запоминающего элемента связан с генератором тактовых импульсов, соединенным через введенный элемент задержки с входом сброса интегратора с обнулением.

ЗО

Источники информации, принятые во внимание при экспертизе изобретения:

1. Маршеж. Операционные усилители и их применение. М., «Энергия», 1974, с. 76 — 77.

З5 2. Смолов В. Б. Аналоговые вычислительные машины. М,, «Высшая школа», 1972, с.

177 — 179 (прототип).

556455

+8 u

Рог 2

Редактор Т. Рыбалова

Заказ 1118/14 Изд. № 414 Тираж 815 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 б ! 1

1 д

Составитель С. Белай

Техред Е. Хмелева Корректор Т, Добровольская