Запоминающее устройство

Иллюстрации

Показать всеРеферат

О П

ИЗОБРЕТЕНИЯ т1 1т 556494

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 03.04.75 (21) 212О281/24 с присоединением заявки № (23) Приоритет

Опубликовано 30.04.77. Бюллетень № 16

Дата опубликования описания 11.05.77 (51) М Кa G 11С 11/00

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 681.327.6 (088.8) (72) Авторы изобретения В. И. Корнейчук, А. В. Городний, С. Н. Аврамова и М. Ф. Чемерица

Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистической революции (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области запоминающих уст|ройств.

Известно запом и нающее устройство, содержащее накопитель, регистр слова, блоки кодирования и декодирования, регистры мощ ности корректирующего кода, дешифратор регист|ров мощности корректирующего кода. Однако в таком запоминающем устройстве применены сложные блоки кодирования и декодирования, а потребление энергии отказавшими ячейками приводит к большим затратам энергии.

Из известных запоминающих устройств наиболее близким техническим решением к изобретению является запоминающее устройство, содержащее адресный олок, вход кото|рого подключен к выходу генератора синхроиьмпульсов, а выход — к входу регистра слова, подключен ному к блоку кодирования, блок декодирования, соединенный через элементы

ИЛИ с |регистром слова, основной и дополнитель ный накопители, информационные входы которых подключены к выходам элементов

И, блок управления и дешиф рато р.

Однако в этом запоминающем устройстве, кроме наличия сложных блоков кодирования и де кодирования и повышен ного потребления энергии, существует сложная система адресации. Это обусловливает большую вероятность ош|ибочной записи информации при пересылке из основ|ного накопителя в допол нительный, что снижаег надежность устройства.

Цель изобретения — повышение надежности

5 устройства.

Это достигается тем, что предлагаемое запоминающее устройство содержит коммутаторы, счетчики, блок переключения питания и дополнительные элементы ИЛИ, входы пер10 ваго коммутатора подключены соответственно к выходам блока кодирования, блока управления, блока декодирова н ия и дешиф ратора, а его выходы — к одним входам элементов И, другие входы которых соединены с выходом

15 ге нерато ра синх роимпульсов. Входы второго коммутатора подключены соответственно к выходам накопителей, блошка управления, блока декодирова ния и дешифратора, а его выходы — к входам блока декодирования, выхо20 ды которого соед|инены с входами первого счетчика. Входы блока переключения питания подключены к выходам,дешифратора и первого счетчика соответстве н но, а его выходы— к управляющим входам накопителей, вход

25 второго счетчика через дополнительные элементы ИЛИ соединен с выходами первого счетчика, а его выход — с входом дешифратор а.

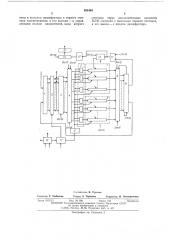

На чертеже показана блок-схема запоми30 на ющего устройства.

556494

Устройство содержит элементы ИЛИ 1, выходы которых подключены к и н фо рмационным входам регистра 2 слова, а выходы последнего к информационным входам блока кодирования 3, первый коммутатор 4, элементы И 5, генератор синхроимпульсов 6, основной на копитель 7, содержащий т регистров сдвига, дополнительный накопитель 8, содержащий n — m регистров сдвига, где т)) n — и.

Устройство также содержит второй коммутатор 9, блок декодирования 10, 1первый счетчик 11, служащий для подсчета количества отказов, блок 12,переключения питания, дополнительные элементы ИЛИ 13, второй счетчик 14, служащий для подсчета номеров заменяющих регистров сдвига, дешифратор 15, блок упра вления 16 и адресный блок 17.

Входы первого коммутатора 4 подключены соответственно .к выходам блока кодированыя

3, блока управления 16, блока декоди рова ния

10 и деш ифратора 15, а его:выходы — к одним входам элементов И 5, другие входы которых соединены с выходом генератора синхроимпульсов 6. Входы второго ком мутатора

9 подключены соответственно к выходам накопителей 7 и 8, блока управления 16, блока декодирования IO и дешифратора 15, à его выходы — к входам блока декод и рования 10, выходы которого соединены с входами .пе рвого счетчика 11. Входы блока 12 переключения питания подключены к выходам,дешифратора

15 и первого счетчика 11 соответственно, а его выходы к управляющим входам накопителей 7 и 8. Вход второго счетчика 14 через дополнительные элементы ИЛИ 13 соединен с выходами первого счетчика 11, а его выход— с входом дешифратора 15.

Устройство работает следующим образом.

Информационное слово через элементы

ИЛИ 1 поступает на регистр 2 слова, а с его выходов — в блок кодирования 3, где в соответствии с информационными разрядами формируются контрольные разряды. С выходов блока кодирования слово подается на входы первого коммутатора 4. С его выходов через элементы И 5 слово поступает на регистры основного накопителя 7 и дополнительного накопителя 8. По другим входам элементов И

5 подаются синхроимпульсы с генератора синхроимпульсов 6, и все разряды слова поступают синхронно в регистры накопителей 7 и

8. Импульсы, поступающие с выхода генератора синхроимпульсов 6 на сдвигающие цепи регистров, обеспечивают синфазный сдвиг информации. Каждый сдвиговый регистр соответствует одному разряду слова, т. е. происходят параллельная запись, сдвиг и считывание слов. С выходов регистров сдвига слово поступает на входы второго коммутатора 9.

С выходов коммутатора 9 слово поступает на блок декодирования 10, который выдает игналы оо отсутствии или наличии ошибки.

С выходов блока декодирования 10 откорректированное слово подается на входы элементов ИЛИ 1. Сигналы о наличии ошибки поступают также на входы первого счетчика 11, где фиксируется количество ошибок каждого регистра основного накопителя 7. По достижении определенного, наперед заданного кода, последний выдает сигнал на блок переключения питания 12 для отключения питания соответствующего регистра (сигнал отключения питания), а сигнал, поступающий в блок 12 из блока 15, управляет включением питания на соответствующий дополнительный регистр, Сигналы с выходов счетчика 11 поступают также через элементы ИЛИ 13 на счетчик 14.

При отказе одного регистра основного накопителя 7 его информация пересылается в первый регистр дополнительного накопителя 8, при отказе другого регистра основного накопителя 7, его информация пересылается во второй регистр дополнительного накопителя

8 и т. д, Дешифратор 15 дешифрирует состояние второго счетчика и выдает управляющие сигналы на коммутаторы 4 и 9. Последние подключают блок кодирования 3 и блок декодирования 10 к исправно работающим регистрам сдвига.

В зависимости от поступивших синхроимпульсов с генератора синхроимпульсов 6 и кода адреса на входы адресного блока 17 последний выдает управляющие сигналы на регистр 2 слова. Под действием этих сигналов слово с выходов регистра слова поступает также и на выходные информационные шины запоминающего блока.

Формула изобретения

Запоминающее устройство, содержащее адресный блок, вход которого подключен к выходу генератора синхроимпульсов, а выход— к входу регистра слова, подключенному к блоку кодирования, блок декодирования, соединенный через элементы ИЛИ с регистром слова, основной и дополнительный накопители, информационные входы которых подключены к выходам элементов И, блок управления и дешифратор, отличающееся тем, что, с целью повышения надежности устройства, оно содержит коммутаторы, счетчики, блок переключения питания и дополнительные элементы ИЛИ, входы первого коммутатора подключены соответственно к выходам блока кодирования, блока управления, блока декодирования и дешифратора, а его выходы — к одним входам элементов И, другие входы которых соединены с выходом генератора синхроимпульсов, входы второго коммутатора подключены соответственно к выходам накопителей, блока управления, блока декодирования и дешифратора, а его выходы — к входам блока декодирования, выходы которого соединены с входами первого счетчика, входы блока переключения питания подклю556404

Составитель В. Рудаков

Техред 3. Тарасова Корректор И. Иозняковская

Редактор Т. Рыбалова

Заказ 1051/15 Изд. Ха 390 Тира>к 735 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, K-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 чены к выходам дешифратора и первого счетчика соответственно, а его выходы — к управляющим входам накопителей, вход второго счетчика через дополнительные элементы

ИЛИ соединен с выходами первого счетчика, а его выход — с входом дешифратора.