Запоминающее устройство

Иллюстрации

Показать всеРеферат

О П И С А Н И Е о0556496

ИЗОБРЕТЕНИЯ

Союэ Саветскик

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 09.09.74 (21) 2058944/24 с присоединением заявки № (51) М. Кл.з б 11С 11/02

Гасударственный комитет (23) Приоритет

Совета Министров СССР по делам изобретений н открытий (53) УДК 628.327.66 (088.8) Опубликовано 30.04.77. Бюллетень № 16

Дата опуоликования описания 11.05.77 (72) Авторы изобретения

Б. Ф. Лаврентьев, А. О. Тимофеев и Л. А. Шумилов

Ленинградский ордена Ленина электротехнический институт им. В. И. Ульянова (Ленина) (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники, Известно запоминающее устройство, содержащее накопитель, элементы, памяти которого состоят из селектирующего и запоминающего сердечников, объединенных резистивным витком связи, (оба сердечника элемента памяти прошиваются числовой шинной, селекти,рующий сердечник — разрядной шинной записи, а запоминающий сердечник — выходной шиной), формирователи числовых токо в, адресный дешифратор, усилители чтения, схемы приема числа, регистр числа, элементы И, ИЛИ, разрядные формирователи записи. Адресный дешифратор соединен с формирователями числового тока, которые подключены к числовым .шинам накопителя. Входы усилителей чтения подключены к выходным ши нам накопителя, а выходы через схемы приема числа соединены с триггерами регистра числа.

Выходы триггеров регистра числа через элементы И и ИЛИ соединены с раз рядБыми формирователями записи.

Наиболее близким техническим решением к изобретению является запоминающее устройство, которое содержит накопитель, формирователь тока записи, выходы которого соединены с одними концами всех разрядных шин накопителя, и нверторы и источники питания.

Для такого запоминающего устройства характерна большая избыточность электронного оборудования, что резко снижает его надежностьь.

5 Для по вышения надежности предлагаемого за поминающего устройства одни входы четных и нверторов подключены к первому источнику питания, одни входы нечетных ияверторов подключены к второму источ|нику пита10 ния, выходы каждой пары четного и нечетного инверторов подключены соответственно к другому концу соответствующей разрядной шины накопителя, другие входы инверторов подключены к соответствующим выходам ре15 гист ра числа.

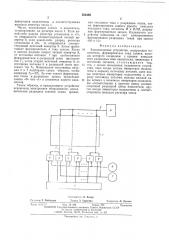

На чертеже показа на блок-схема предлагаемого запоминающего устройства.

Запоминающее устройство содержит регист1р числа 1,,накопитель 2, прошитый раз20 рядными шинами 3, формирователь 4 тока записи, выход 5 которого соединен с одними концами всех разрядных шин накопителя, источни1ки питания 6 и 7, четные 8 и нечетные

9 инвBlpTopbI. Выходы каждой пары четного и

25 нечетного инверторов,подключены соответствен но к другому концу соответствующей разрядной шины 3 накопителя 2. Одни входы четных инверторов 8 подключены к источнику питания 7, а входы нечетных инверторов 9—

30 к источнику питания 6. Другие входы всех

556496

L..

Составитель В. Вакар

Текред 3. Тарасова

Корректор Л. Орлова

Ред: ктор Т. Рыбалова

Заказ 1051/!7 Изд. № 390 Тираж 735 Подписное

Ц1-1ИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Я(-35, Раушскап наб., д. 4/5

Типографии, р. Сапунова, 2 инверторов подключены к соответствующим выходам регистра числа 1.

Число, подлежащее записи в накопитель, устанавливают на регистре числа 1. Если какой-либо разряд регистра установлении в «1», то открывается соответствующий четный инве ртор 8, если какой-либо разряд;регистра установлен в «0», то открывается соответствующий нечетный инвертор 9. Затем срабатывает формирователь 4 тока записи. Когда в данном разряде открыт четный инвертор 8, от источника питания 7 при срабатывании формирователя в 1разрядной шине п ротекает ток Т1, когда открыт нечетный инвертор 9, от источника питания б в разрядной шине протекает ток Тз. Напряжения источников питания 6 и 7 подбирают таким образом, чтобы например Т2=!2T . За счет такого фо рмирования токов в 1разрядных шинах происходит запись «О» или «1» в элементах памяти накопителя.

Таким образом, в .предлагаемом устройстве исключены электронное оборудование, дополн ительное разрядное сечение, схема сравнения числового тока с разрядным током, схема фо рми рования заднего фронта импульса числового тока, элементы И и ИЛИ, разрядные формирователи записи. Надежность уст5 ройства повышена за счет одновременного формирования разрядных токов при записи

«О» и «1».

Формула изобретения

10 Запоминающее устройство, содержащее накопитель, формирователь тока записи, выходы которого соединены с одними концами всех разрядных шин накопителя, и нверто ры и источники питания, отличающееся тем, 15 что, с целью, повышения надежности устройства, одни входы четных инверторов подключены к первому источнику питания, одни входы нечетных <инверторов подключены к второму источнику питания, выходы каждой па20 ры четного и нечетного инверто ров подключены соответственно к другому концу соответствующей разрядной шины накопителя, другие входы ин верторов подключены к соответствующим выходам регистра числа.