Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

00 556498

Саюа Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 04.03.75 (21) 2110938/24 с присоединением заявки №вЂ” ,(23) Приоритет

Опубликовано 30.04.77. Бюллетень № 16

Дата опубликования описания 11.05.77 (51) М Кт а 6 11С 17/00

Государственный комитет

Совета Министров СССР (53) УДК 681.327.66 (088.8) ло делам изобретений и открытий (72) Авторы изобретения

В. П. Деркач, В. М. Корсунский, М. И. Васюхин и Г, 3. Карманов (71) Заявители

Ордена Ленина институт кибернетики АН Украинской ССР и Научно-исследовательский институт автоматики (54) ПОСТОЯ H НОЕ ЗАПОМИ НАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области .вычислительной техники и п редназ начено для хранения и адресной выборки фиксирован ной информации (микротврограмм, значений констант и табличных фунтоций и т. д.).

Известны постоянные запоминающие устройства (ПЗУ), .содержащие числовой блок, вьвполненный в виде диод ной матрицы, регистр адреса, деш ифр атор и усил ител и считывания.

Одно из известных ПЗУ содBp?KHT числовой бло1к, выполненный в виде диодной матрицы, одни ши ны которого подключены к выходам дешифратора, а другие — к разделительным элементам (резисто рам) .

Недостатком этого ПЗУ является низкое быстродействие.

Наиболее близким техническим решением

1к изобретению является уст|ройство, содержащее,регистр адреса, выходы одной группы разрядов которого подключены к входам дешиф1рато ра, выходы дешиф|ратора подключены к о дним ш инам числового блошка, выполHBHíoão в,в иде дио.дной,матрицы, дру,гие,шины кото рого подключены к разделительным элементам, выходные диодные сборки, выходы которых подключены к усилителям считывания, и дополнительные диодные сборки.

Для этого уст|ройства ха ра ктерны органичен ное быстродействие, связанное с тем, что разделительные элементы (резисторы) включены .в цепь,за ряда — разряда паразитных емкостей всех ooipamo смещенных диодов числового блока, и недостаточно высокая надежность при интегральном иопол не нии числового блошка из-за отсутствия при нем встроенного диодно-резистивного адресного блока, что предопределяет значительное количество выводов из тористалла и соответстве н но излишне

10 большое число паек,при сборке,ПЗУ.

Цель изобретения — повышение бьгстродействия и надеж)ности известного ПЗУ.

Это достигается тем, что предлагаемое устройство, содержащее регистр адреса,:выходы

)5 одной группы, разрядов которого подключе ньт к входам дешифрато ра, выходы дешифрато ра подключены к одним шинам числового блока, выполненного в виде диодной матрицы, другие шины которого подключены к разделительным элементам, выходные диодные сборки, выходы которых .подключены к усилителям считывания, и дополнительные диодные сборки, содержит в числовом блоке дополнительную диод1ную матрицу, шины которой, соединяющие катоды диодов, .подключены к выходам другой группы разрядов регистра адреса, а шины, соединяющие аноды диодов, подключены к разделительным элементам и к входам выходных и дополнительных диодных

30 сборок.

556498

30

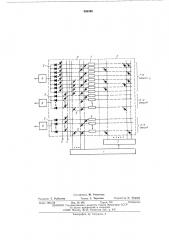

На чертеже показа на блок-схема, устройства.

Устройство содержит регистр адреса 1, выходы одной группы, разрядов,которого подключены к входам дешифратора 2, выходы дешиф ратора подключены к одним шинам числового блока 3, выполненного в виде диод ной матрицы, состоящей из и секций. Устройство содержит также в числовом блоке дополнительную диодную матрицу 4, состоящую из и секций, шины которой, соединяющие катоды диодов, подключены к другой группе разрядов .регистра адреса 1, а шины, соединяющие аноды диодов, подключены .к входам выходных 5 и дополнитель|ных 6 диодных сборок и к разделительным, элементам (резисторам) 7. Выходы выходных диодных сборок 5 подключены к усилителям считывания 8.

Предложенное устройство работает следующим об разом.

В соответствии с состоянием первой группы .разрядов регистра адреса 1 дешифратор

2 подает на од ну из подключенных к нему вертикальных шин числового блока 3 высокий потенциал. Через все диоды, подключенные к выбранной вертикальной шине, этот потенциал передается .на резисторы 7. В дополнительной диодной матрице 4 диоды 9 выключены так, что,п ри любом состоякии другой группы разрядов регистра ад|реса 1 только одна из горизонтальных шин в каждой секции остается не заземленной, и на выходную диодную сборку 5 пропускается сигнал считывания только с соответствующей шины.

Если в дан ной секции числового блока 1 на пересечении выбора иной вертикальной и выбранной горизонтальной шин включен диод, то на соответствующий усилитель считывания

8 через этот диод, резистор 7 и выходную диод ную сборку поступает высокий потенциал.

Если в выбранном пересечении диода нет, то на соответствующий усилитель считывания 8 высокий потенциал не поступает, так как остальные горизонтальные ши ны данной секции,заземлены через диоды до пол нительной диодной MBTlpHIIbI 4. У казанные процессы происходят одновременно во всех секциях числового блока,3 и дополнительной диодной мат,рицы 4, в результате чего из ПЗУ параллельно считывается и-разрядное д воичное число.

П(ри построении ПЗУ,:работающих с сигналами отрицательной поляр ности, на правления выключения диодов в обеих диодных матрицах и в диодных сборках должны быть изменены на противоположные, а деши ф ратор и вторая группа, разрядов регистра адреса должны,подавать на соответствующие шины напряжения отрицательной полярности.

В предложенном ПЗУ резисторы 7 включены в цель заряда — раз рядa .паразитных емко стей обратно смещенных диодов только дополнительной диодной матрицы и диодных сборок, суммарная емкость которых намного ме ньше суммарной паразитной емкости числового блока, и за счет этого достигается большее быстродействие. Паразитные емкости диодов числового блока заряжаются (разряжаются) через транзисторные, ключи, имеющие малое сопротивление. Кроме того, дополнительная диодная,матрица при интегральном исполнении вместе с числовым блоком на одном кристалле обеспечивает внутреннюю расшифровку части кода адреса, что приводит к заметному уменьшению,количества выводов из кристалла микросхемы, сокращает число паек при сборке и повышает надежноо сть П 3 У.

Формула изобретения

Постоя нное,запоминающее устройство, содержащее регистр адреса, выходы одной г руплы разрядов которого подключены к входам дешифратора, выходы дешиф ратора подключены к одним шинам числового блока, .выполненного в виде диодной матрицы, другие шины которого подключены к разделительным элементам, выходные диодные сборки, выходы которых лодключены к усилителям считывания, и дополнительные д иод ные сборки, отличающееся тем, что, с целью повышения быстродействия и .надежности устройства, оно содержит в числовом блоке дополнительную,диод ную матрицу, шины которой, соединяющие катоды диодов, подключены к выходам другой груп пы разрядов релистра адреса, а .шины, соединяющие аноды диодов, .подключены к разделительным элементам и к входам выходных и дополнительных диод|ных сборок.

556498

2-Я

СР/Щ /Я л-Я

СС//Ц//Я

Составитель Ю. Розенталь

Редактор Т, Рыбалова

Заказ 1051/19 Изд. № 390 Тираж 735 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, /К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Текред 3. Тарасова Корректор О. Тюрина

cg/где/Iя