Ячейка памяти регистра сдвига

Иллюстрации

Показать всеРеферат

,() ф56499

ОПИС М

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 28.01.75 (21) 2100384/24 с присоединением заявки Ке (51) М. Кл.- С 11С 19/00.

Совета Министров СССР ло делам изобретений (53) УДК 681.327.66 (088.8) Опубликовано 30.04.77. Бюллетень Хо 16

Дата опубликования описания 27.05.77 и открытий (72) Авторы изобретения

A. Ф. Авдон!!т!, O. Г. Дашко и В. П. Молоч!тев (71) Заявитель (54) ЯЧЕЙКА ПА!т1ЯТИ ДЛЯ РЕГИСТРА СДВИГА

Государственным комитет (23) Приоритет

Изобретение относится к вычислительной технике и может быть применено в телемеханике и устройствах связи, Известны ячейки памяти для регистра сдвига, которые содержат по одному триггеру, Переключение триггеров всех ячеек осуществляется одновременно общим тактовым сигналом, длительность которого должна быть меньше времени переключения триггеров, что снижает надежность устройства.

Известны ячейки памяти для регистра сдвига, содержащие по два триггера, переключение которых разнесено во времени и осуществляется двумя тактовыми, сигналами по двум разным шинам. Это устройство более надежно, но в нем на запоминание единицы информации требуются два триггера, что усложняет устройство.

Из известных наиболее близкой по технической сущности является ячейка памяти для регистра сдвига, содержащая тиггер, единичный и нулевой выходы которого соединены с выходами ячейки памяти, информационные входы которой подключены к управляющим входам триггера соответственно, В этой ячейке памяти информационный и тактовый каналы совмещены, при этом используется троичная система входных сигналов, что усложняет устройство, так как информация при полном заполнении регистра может располагаться только через ячейку и требует удвоенного числа ячеек памяти. Кроме того, в ячейке не контролируется заносимая информация, что снижает надежность

5 устройства.

Цель изобретения — повышение надежности ячейки памяти.

Это достигается тем, что в ячейку памяти введены элементы И, ИЛИ, РАВНОЗНАЧ-!

О НОСТЬ и ЗАПРЕТ, первый вход которого соединен с одним из входов элемента И и выходом элемента ИЛИ. Второй вход элемента ЗАПРЕТ подключен к тактовому входу ячейки памяти и другому входу элемента И, 15 выход которого подсоединен к тактовому выходу ячейки памяти и к одному из входов элемента ИЛИ, другой вход которого соединен с выходом элемента РАВНОЗ НАЧНОСТЬ. Один из входов элемента РАВНО20 ЗНАЧНОСТЬ подключен к единичному выходу триггера, один из информационных входов которого соединен с другим входом элемента РАВНОЗНАЧНОСТЬ, а тактовый вход триггера подключен к выходу элемента ЗА25 ПРЕТ.

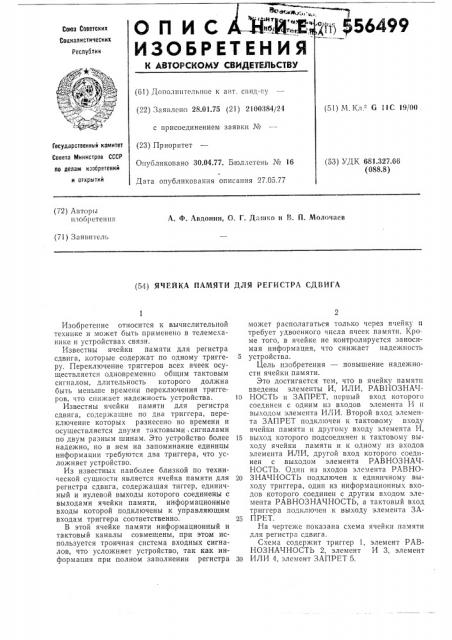

На чертеже показана схема ячейки памяти для регистра сдвига.

Схема содержит триггер 1, элемент РАВНОЗНАЧНОСТЬ 2, элемент И 3, элемент

30 ИЛИ 4, элемент ЗАПРЕТ 5.

556499

Зо

Работает ячейка памяти следующим образом.

Сигнал с входа воспринимается ячейкой памяти как команда на занесение входной информации в триггер 1. После обработки этой команды на выходе ячейки памяти появится сформированный элементом И 3 сигнал «Исполнение». Если, например, состояние триггера 1 ячейки памяти в момент прихода команды «Занесение» на управляющий вход ячейки памяти не соответствует значению сигнала на информационном входе этой ячейки, то состояние триггера 1 изменяется путем записи в него информации.

Сигнал управления записью подается на синхронизирующий вход триггера 1, а формируется элементом ЗАПРЕТ 5. После переключения триггера 1 его состояние соответствует входной информации и на выходе элемента РАВНОЗНАЧНОСТЬ 2 возникает сигнал тождественности, который через элемент

ИЛИ 4 воздействует на элемент ЗАПРЕТ 5, который в свою очередь снимает сигнал управления записью с синхронизирующего входа триггера 1. Элемент РАВНОЗНАЧНОСТЬ

2, элемент ИЛИ 4, элемент ЗАПРЕТ 5 и триггер 1 образуют замкнутый контур, где элемент РАВНОЗНАЧНОСТЬ 2 является датчиком обратной связи по исполнению, триггер 1 — объектом управления, а элемент

ЗАПРЕТ 5 служит для управления триггером.

Если в момент поступления команды «Занесение» состояние триггера 1 уже соответствует входной информации, то необходимости переключать триггер 1 нет, для чего имеющийся на выходе элемента РАВНОЗНАЧHOCTb 2 сигнал тождественности через элемент ИЛИ 4 запрещает управление триггером 1. Элемент И 3 при наличии сигнала с элемента РАВНОЗНАЧНОСТЬ 2 и команды

«Занесение» формирует сигнал «Исполнение», поступающий на выход ячейки памяти. Сигнал «Исполнение» означает окончание операций в ячейке памяти и установление прямого соответствия между входной информацией и информацией, содержащейся в ячейке памяти, Связь выхода элемента И 3 со своим входом через элемент ИЛИ 4 необходима для надежной работы ячейки в регистре сдвига, Сигнал «Исполнение» с выхода ячейки памяти поступает на управляющий вход другой ячейки памяти и является для нее командой

«Занесение». Все процессы в этой ячейке памяти будут происходить аналогично описанным выше в соответствии с ситуацией. После обработки команды «Занесение» другой ячейкой памяти на ее выходе появится сигнал

«Исполнение», который поступит на управляющий вход первой ячейки памяти. Сигнал

«Исполнение» с выхода первой ячейки памяти поступает на выход, что означает окончание процесса сдвига информации в регистре на один разряд, запись в первую ячейку памяти нового разряда информации, отсутствие сбоев информации при сдвиге, т. е. нормальную работоспособность всех ячеек памяти регистра. Время распространения фронта сигнала определяется временем срабатывания элементов образующейся цепочки, т. е. максимально используется их быстродействие.

Изобретение позволяет при использовании предельного быстродействия элементов упростить регистр сдвига, сократив число ячеек в два раза, и увеличить надежность посредством самоконтроля работоспособности регистра.

Формула изобретения

Ячейка памяти для регистра сдвига, содержащая триггер, единичный и нулевой выходы которого соединены с выходами ячейки памяти, информационные входы которой подключены к управляющим входам триггера соответственно, отл и ч а юща я ся тем, что, с целью повышения надежности ячейки памяти, в нее введены элементы И, ИЛИ, РАВНОЗНАЧНОСТЬ и ЗАПРЕТ, первый вход которого соединен с одним из входов элемента

И и выходом элемента ИЛИ, второй вход элемента ЗАПРЕТ подключен к тактовому входу ячейки памяти и другому входу элемента И, выход которого подсоединен к тактовому выходу ячейки памяти и к одному из входов элемента ИЛИ, другой вход которого соединен с выходом элемента РАВНОЗНАЧНОСТЬ, один из входов элемента РАВНОЗНАЧНОСТЬ подключен к единичному выходу триггера, один из информационных входов которого соединен с другим входом элемента РАВНОЗНАЧНОСТЬ, а тактовый вход триггера подключен к выходу элемента ЗАПРЕТ.

556499! !

1 Г! l

Составитель А. Воронин

Техред 3. Тарасова

Редактор T. Рыбалова

Корректор О. Данишева

Типография, пр. Сапунова, 2

Заказ 999/12 Изд. № 392 Тираж 735 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5