Оперативное запоминающее устройство с блокировкой неисправных запоминающих элементов

Иллюстрации

Показать всеРеферат

!

» .. - -""элло т!эн !:41- ..

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ р>556502

Союз Советскик

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, свид-ву (22) Заявлено 09.06.75 (21) 2142224/24 с присоединением заявки № (23) Приоритет

Опубликовано 30.04.77. Бюллетень № 16

Дата опубликования описания 30.05.77 (51) М Кч С 11С 29/00

Гасударственный комитет

Совета Министров СССР ва делам, изобретений и открытий (53) УДК 681.327,6 (088.8) (72) Авторы изобретения

О. А. Терзян и Л. M. Чахоян (71) Заявитель (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

С БЛОКИРОВКОЙ НЕИСПРАВНЫХ ЗАПОМИНАЮЩИХ

ЭЛЕМЕНТОВ

Изобретение относится к запоминающим устройствам.

Известны оперативные запоминающие устройства с блокировкой неисправных запоминающих элементов.

Одно из известных устройств содержит регистр адреса, соединенныи через дешифратор адреса с накопителем, регистр слова, разделенный на группы разрядов, дополнительный накопитель с резервными группами разрядов, блок управления, блок контроля четности по группам разрядов, блок переадресации неисправных групп разрядов с самоконтролем, первые входы которого подключены к выходам регистра адреса, одни выходы — к соответствующим группам разрядов регистра слова и дополнительного накопителя, а другие выходы — к адресным входам дополнительного накопителя. недостатком этого устройства является то, что в нем блокируются только выявленные заранее отказавшие группы запоминающих элементов ячеек и не происходит их автоматической блокировки в процессе работы устройства, что значительно снижает надежность устройства. Из известных устройств наиболее близким техническим решением к изобретению является оперативное запоминающее устройство с блокировкой неисправных запоминающих элементов, содержащее регистр адреса, соединенный через дешифратор адреса с основным накопителем, регистр слова, подключенный к первому блоку контроля, основному и дополнительному накопителям, блок переадресации неисправ5 ных групп разрядов, соединенный с регистром адреса, регистром слова, дополнительным накопителем и счетчиком, блок управления, кодирующий блок и элементы «И» и «ИЛИ», второй блок контроля. В этом устройстве про10 исходит блокировка группы запоминающих элементов отказавшей ячейки памяти. Недостатком устройства является его невысокая эффективная емкость.

Цель изобретения — повышение надежно15 сти устройства. 1!оставленная цель достигается тем, что входы второго блока контроля подключены к выходам блока переадресации неисправных групп разрядов, а выход — ко входу блока управления и одному из входов

20 блока переадресации неисправных групп разрядов, другие входы которого соединены с выходами первого блока контроля, входами первого элемента «ИЛИ», кодирующего блока и одними входами первых элементов «И», вы25 ходы которых подключены ко входам второго элемента «ИЛИ», выходы блока переадресации неисправных групп разрядов соединены с другими входами первых элементов «И» и со входами третьего элемента «ИЛИ», выхо30 ды элементов «ИЛИ» через вторые элементы

556502

СО

3

«И» подключены соответственно ко входам блока управления и блока переадресации неисправных групп разрядов, выход счетчика соединен с одним из входов кодирующего блока, а входы счетчика — с выходами второго элемента «ИЛИ» и блока управления соответственно.

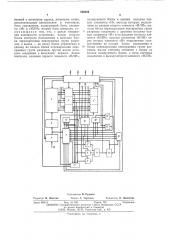

На чертеже приведена блок-схема предложенного оперативного запоминающего устройства с блокировкой неисправных запоминающих элементов.

Устройство содержит регистр 1 адреса, дешифратор 2 адреса, основной накопитель 3, регистр 4 слова, дополнительный накопитель

5, содержащий резервные группы разрядов, блок управления 6, блок 7 переадресации неисправных групп разрядов, выполненный, например, в виде ассоциативного запоминающего блока, первый блок 8 контроля, например, осуществляющий проверку четности по группам разрядов, первые элементы «И» 9, первый 10 и второй 11 элементы «ИЛИ», счетчик 12, третий элемент «ИЛИ» 13, вторые элементы «И» 14 и 15, кодирующий блок 16 и второй блок 17 контроля.

Входы регистра 1 адреса соединены с шинами 18 адреса, а выходы соединены с входами блока i и через дешифратор 2 — с накопителем 3, выходы которого соединены с входами регистра 4. Выходы последнего подключены к входам накопителей 3 и 5, блока

8 контроля, а также к выходным шинам 19.

Входы второго блока 17 контроля подключены к выходам блока 7, а выход — ко входу блока 6 управления и одному из входов блока 7, другие входы которого соединены с выходами первого блока 8 контроля, входами элемента «ИЛИ» 10, кодирующего блока 16 и одними входами первых элементов «И» 9, выходы которых подключены ко входам элемента «ИЛИ» 11, выходы блока 7 соединены с другими входами элементов «И» 9 и со входами элемента «ИЛИ» 13, выходы элементов

«ИЛИ» 10, 11 и 13 через элементы «И» 14 и

15 подключены соответственно ко входам блока б управления и одному из входов блока 7, выход счетчика 12 соединен с одним из входов кодирующего блока 16, а его вход — с выходом элемента «ИЛИ» 11.

Устройство работает следующим образом.

Код адреса по шине 18 поступает на регистр 1, затем после подачи сигнала обращения (записи или считывания) в блок управления 6 начинается цикл записи или считывания информации. Рассмотрим вначале цикл считывания. При обращении по исправному адресу работа устройства происходит как обычно: выбранное с помощью дешифратора

2 слово из накопителя 3 поступает на регистр

4 и затем на выходные шины 19 и входы блока 8. В этом случае информация с выходов блока 7 и выходов блока 8 отсутствует, и блок управления б выдает сигнал об окончании цикла считывания.

4

При возникновении в процессе считывания сбоя или повреждения в запоминающих элементах, приводящих к искажению информации в слове (одном или нескольких разрядах), блок 8 обнаружит ошибку и выдаст сигнал об этом в блок управления б, который начнет выполнять программу, выясняющую, произошел сбой или отказ (например, многократным считыванием по одному и тому же адресу). При обнаружении сбоя блок б выдает сигнал об этом, исправную информацию по швам 19 и сигнал конца обращения. Однако, если произошел отказ, блок 6 выдает сигнал, согласно которому не может продолжаться работа по данной программе и необходимо либо часть программы выполнить заново с определенного ее участка, либо определенную часть программы заново занести в устройство извне.

При обнаружении отказа блок управления

6 выдает также сигналы, сохраняющие информацию на регистрах 1 и 4, производит запись кода неисправного адреса в признаковую часть блока 7 и адрес соответствующей резервной группы разрядов дополнительного накопителя 5 в информационную часть блока 7.

Рассмотрим подробнее как происходит формирование кода адреса резервной группы разрядов дополнительного накопителя 5 и оптимальное заполнение его объема. Накопитель 5 содержит несколько (на чертеже три) резервных групп разрядов, поэтому адрес любой резервной группы разрядов должен состоять из адреса слова в накопителе 5 и указания, какая из групп разрядов данного слова замещает отказавшую. Адрес слова задается счетчиком 12 в двоичном коде, а информация, указывающая замещающую резервную группу разрядов, формируется блоком 8 контроля, определяющим работоспособность каждой группы разрядов, и заносится в разряды информационной части блока 7.

Число таких разрядов в блоке 7 равно числу групп разрядов в слове дополнительного накопителя 5.

Для того, чтобы заполнение дополнительного накопителя 5 было оптимальным, необходимо, чтобы резервные группы разрядов подключались в работе с основным накопителем по такому закону, который бы позволял использовать все резервные группы разрядов дополнительного накопителя 5, но при этом не требовалось бы периодической перекомпоновки размещенной в блоке 7 информации.

Цели оптимального заполнения служат элементы «И» 9, 14 и 15 и «ИЛИ» 10, 11 и 13, а также специальная программа, реализуемая блоком управления 6 и счетчиком 12. С этой же целью при занесении в признаковую часть блока 7,кода неисправного адреса в эту же ячейку признаковой части заносится и адрес слова дополнительного накопителя, который задается счетчиком 12.

556502

40 об

Всякое новое занесение информации в блок

7 выполняется по следующей программе.

Сначала в признаковой части блока 7 маскируется код адреса основного накопителя, и считывание происходит по адресу (начиная с нулевого), выдаваемому счетчиком 12. При этом происходит анализ содержимого разрядов, указывающих на неисправность групп разрядов. Если происходит совпадение информации, записанной ранее в этих разрядах, с информацией на выходах блока 8, то по данному адресу накопителя 5 нельзя использовать резервную группу и в счетчик под действием сигналов от элемснта «ИЛИ» 11 и блока б добавляется «1» и снова производится считывание из блока 7 разрядов признаков неисправности, и так до тех пор, пока на выходе элемента «ИЛИ» 11 и не будет отсутствовать сигнал совпадения. Тогда блок 6 начнет заносить информацию от регистра 1 и счетчика 12 в признаковую часть и информацию от блока 8 и счетчика 12 в информационную часть блока 7. После записи очередного адреса резервной группы разрядов блок б выдает сигнал окончания процесса. Устройство снова готово к выполнению своих функций.

При считывании из устройства код адреса, поступивший на регистр 1, проверяется на наличие его в блоке 7 (при этом маскируется код адреса от счетчика 12) и при совпадении блок 7 выдает соответствующий код резервной группы (или групп) разрядов в дополнительном накопителе 5, из которого параллельно с исправными группами разрядов основного накопителя на регистр 4 поступит считываемая информация. Если она исправна, то блок 6 выдает сигнал окончания операции считывания и информацию по шинам 19.

Однако, если при считывании информации из основного накопителя 3 и резервных групп разрядов снова обнаружится отказ, то возмо1кны две причины: либо возник отказ в какой-либо другой группе разрядов слова основного накопителя 3, либо отказал запоминающий элемент в используемой в данной операции резервной группе.

В первом случае, который будет обнаружен по сигналу от элемента «И» 15 (при отсутствии сигнала на выходе элемента «ИЛИ» 11), блок управления 6 выдает сигнал, который полностью освободит в блоке 7 ячейку (т. е. сотрет информацию в ее признаковой и информационной частях), к которой только что произошло обращение. После чего выполняется с самого начала описанная выше программа занесения информации переадресации в блок 7, т. е. счетчик 12, управляемый блоком 6 и сигналами от элемента «ИЛИ» 11, начнет последовательный нсребор адресов (начиная с нулевого), найдет свободную ячейку

В дополнительном накопителе 5 и выдаст ее адрес в блок 7. Таким образом, -юбой неиспоавный код адреса устройства находится в признаковой части блока 7 только в одной

5;1

6 ее ячейке. Нетрудно видеть, что при выполнешги такой программы при записи информации в блок 7 объем дополнительного накопителя 5 используется наиболее оптимально и не требуется периодической перекомпоновки содержимого блока 7.

В случае отказа запоминающего элемента в резервной группе разрядов элемент «И» 15 снова выдает сигнал о необходимости освобо11,дсн,"„., ячейки блока 7 от записанной в ней информации переадресации и блок 6 начинает производить очистку (стирание) данной ячейки. Однако в этом случае происходит стирание не всей информации, записанной в данной ячейке, а только кода неисправного адреса накопителя 3, записанного в признаковой части блока 7. Вся ocTBльная информация (т. е. вся информационная часть и код адреса дополнительного накопителя 5, записанный в признаковой части ячейки блока 7) остается без изменения, так как их стирание запрещается сигналом на выходе элемента

«1: » 1-4, ao3HII caioIIIHxi iipH 0TIIBBB запоминающего элемента в резервной группе разрядов.

Cохране1ыая таким образом информация в ячейке блока 7 при цикле очередной записи информации в блок 7 запрстит использование отказавшей резервной группы разрядов. 3атем блок 6 снова начинает цикл занесения информации iiepeapccBIIHII в блок 7. Таким образом, предложенное устройство позволяет аи1о:, атически осущестьлять блокировку неисправных групп разрядов, возникающих в ходе работы как в основном накопителе 3, так и в дополнительном н копителе 5.

Отказы запоминающих элементов могут возниicd IH H cB:BIO ; б;1оке i переадресации H(исправных групп разрядов, причем эти отказы не будут обнаруживаться блоком 8. Поэтом целесообразно использовать блок 7 с самоконтролем, в котором происходит автоматическая блокировка неисправных ячеек.

Зто осуществляется следующим образом.

11ри записи информации в блок 7 блоком

16 формируется ее код четности, который также заносится в блок 7. При считывании информации из блока 7 она проверяется на четность блоком 17, сигналом об ошибке которого в специальный разряд неисправности ячейки олока 7 (после установления наличия отказа) заносится признак, запрещающий обращение к этой ячейке. После этого блок 6 снова начинает цикл записи информации переадресации в новую ячейку блока 7 по описанной вышс программе.

Формула изобретения

Оперативное запоминающее устройство с блокировкой неисправных запоминающих элс:аептов, содержащее регистр адреса, сое1иненнь111 через дешнф11а! Ор адреса с Основ"

;1ЫМ ildii011;ITC iP ii> РЕГHCTP C OIIB, IIOQKJIIO ICHпый li пе1чвом1 б,1ок1 контроля, Осllовному и дополнительному накопителям, блок переадресации неисправных групп разрядов, соеди556502

Составитель В. Рудаков

Текред 3. Тарасова

Корректор О. Данишева

Редактор В. Левятов

Заказ 999/14 Изд. № 392 Тираж 735 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, К-35, Раушская наб., д. 4/5 типография, пр. Сапунова, 2 ненный с регистром адреса, регистром слова, дополнительным накопителем и счетчиком, блок управления, кодирующий блок, элементы «И» и «ИЛИ», второй блок контроля, о тличающееся тем, что, с целью повышения надежности устройства, входы второго блока контроля подключены к выходам блока переадресации неисправных групп разрядов, а выход — ко входу блока управления и одному из входов блока переадресации неисправных групп разрядов, другие входы которого соединены с выходами первого блока контроля, входами первого элемента «ИЛИ», кодирующего блока и одними входами первых элементов «И», выходы которых подключены ко входам второго элемента «ИЛИ», выходы блока переадресации неисправных групп разрядов соединены с другими входами первых элементов «И» и со входами третьего элемента «ИЛИ», выходы элементов «ИЛИ» через вторые элементы «И» подключены соответственно ко входам блока управления и блока переадресации неисправных групп разрядов, выход счетчика соединен с одним из входов кодирующего блока, а вход счетчика подключен к выходу второго элемента «ИЛИ».