Устройство для выделения рекуррентных сигналов фазового пуска в многоканальных системах связи

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ пп 55656l

Соиiз QOBBTMHx

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 14.06.74 (21) 2034294/09 с присоединением заявки ¹ (23) Приоритет

Опубликовано 30.04.77. Бюллетень № 16

Дата опубликования описания 20.06.77 (51) М. Кл Н 04L 7/02

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.394.622.2 (088.8) (72) Авторы изобретения

И. Ф. Хомич, Л. П. Трясогузов и В. Г. Каминскт)1й 1T5

Пензенский завод-ВТУЗ при заводе ВЭМ (Филиал Пейзенского —— политехнического института) ",, ЯЯ п л и эиЕГ а (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ РЕКУРРЕНТНЫХ

СИГНАЛОВ ФАЗОВОГО ПУСКА В МНОГОКАНАЛЬНЫХ

СИСТЕМАХ СВЯЗИ

Изобретение относится к радиотехнике и может использоваться в устройствах синхронизации в многоканальных системах связи.

Известно устройство для выделения рекуррентных сигналов фазового пуска в многоканальных системах связи, содержащее накопитель знаков, соединенный с дешифратором пусковых комбинаций и блоком сумматоров по модулю два, выход которого подключен к схеме сравнения и накопителю знаков 1).

Однако это устроиство не обладает достаточным быстродействием.

Целью изобретения является повышение быстродействия. ,Цля этого в устройство для выделения рекуррентных сигналов фазового пуска в многоканальных системах связи, содержащее накопитель знаков, соединенный с дешифратором пусковых комбинаций и блоком сумматоров по модулю два, выход которого подключен к схеме сравнения и накопителю знаков, введены буферные элементы, коммутатор, накопитель результатов и последовательно соединенные сумматор, дешифратор пороговых значений и блок управления, подключенный к управляющим входам коммутатора, накопителя знаков и накопителя результатов, выход которого соединен с входом сумматора, к второму входу которого подключена схема сравнения, при этом буферные элементы подключены к коммутатору, выход которого соединен с сигнальным входом накопителя знаков и вторым входом схемы сравнения, а дешифратор пусковых комбинаций подключен к блоку управления, причем выход сумматора соединен с входом накопителя результатов.

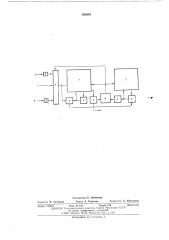

На чертеже приведена структурная электрическая схема устройства для выделения реккурентных сигналов фазового пуска в многоканальных системах связи.

Устройство содержит накопитель 1 знаков, выход которого соединен с входами дешифратора 2 пусковых комбинаций и блока сумматоров 3 по модулю два, выход которого сое15 динен с входами схемы 4 сравнения и накопителя 1 знаков; буферные элементы 5, выходы которых соединены с входами коммутатора 6; накопитель 7 результатов; последовательно соединенные сумматор 8, дешифратор 9 поро2О говых значений и блок 10 управления, выход которого соединен с входами коммутатора 6, накопителя 1 и накопителя 7, выход которого соединен с входом сумматора 8, к второму входу которого подключена схема 4, при этом

25 выход коммутатора 6 соединен с сигнальным входом накопителя 1 и вторым входом схемы

4, а дешифратор 2 подключен к блоку 10 управления, причем выход сумматора 8 соединен с входом накопителя 7.

ЗО Устройство работает следующим образом.

556561

Принимаемые по параллельным каналам связи двоичные знаки посылок через буферные элементы 5 и коммутатор 6 поступают в накопитель 1, где запоминаются в оперативном запоминающем устройстве (ОЗУ). Последовательность подключения N каналов задается блоком 10 управления в зависимости от числа и приоритетности каналов связи, а также скорости передачи информации.

Ьлок 10 легко реализуется на логических элементах в соответствии с заданным алгоритмом работы.

Для каждого канала связи в соответствующих зонах ОЗУ хранится и двоичных знаков посылки фазового пуска, где и — степень образующего многочлена рекуррентной последовательности (РП), что достаточно для рекуррентной проверки и образования последующих знаков посылки при автономном генерировании знаков. Для рекуррентной проверки из

ОЗУ накопителя 1 в олок сумматоров 3 поступают знаки, соответствующие ненулевым . коэффициентам образующего многочлена РП.

На выходе схемы 4 сравнения появляется сиг: нал при удовлетворении рекуррентной проверки знака, принимаемого из канала связи. Зти сйтналы поступают на сумматор 8, который осуществляет суммирование их в двоичном коде с m-разрядным числом, хранящимся в накопителе 7 и соответствующим результатам предшествующих проверок для данного канала.

Разрядность сумматора 8 выбирается из следующего соотношения:

Ри ) 1оя2 (где К вЂ” пороговое значение серии проверок знаков на соответствие рекуррентному закону.

Дешифратор 9 выдает сигнал в блок 10 управления в том случае, если для данного канала значение т-разрядной суммы превышает пороговое значение, который прекращает цикл опроса анализируемого канала по входу, включает цепь автономной генерации знаков РП: выход накопителя 1 — блок 3, и подключает дешифратор 2.

Выделенный сигнал фазового пуска переводит блок 10 в исходный режим работы данного канала или при необходимости — к пе20

45 реходу к обслуживанию других дополнительных каналов связи.

Таким образом, сумматор 8 в совокупности с дешифратором 9 и накопителем 7 обеспечивает подсчет рекуррентных проверок для всех

Nпараллельных каналов,,т. е. выполняет функции N счетчиков серии совпадений. Кроме того, накопитель 1 в совокупности с коммутатором 6 и блоком 10 обеспечивает прием посылок фазового пуска с соответствующими проверками по всем параллельным каналам, т. е. выполняет функции У регистров сдвига с переключателями режима работы и селекторами фазирующих сигналов. В результате этого существенно уменьшается объем оборудования при сохранении общего числа параллельно включенных каналов связи.

Формула изобретения

Устройство для выделения рекуррентных сигналов фазового пуска в многоканальных системах связи, содержащее накопитель знаков, соединенный с дешифратором пусковых комбинаций и блоком сумматоров по модулю два, выход которого подключен к схеме сравнения и накопителю знаков, о т л и ч а ю щ е еся тем, что, с целью повышения быстродействия, в него введены буферные элементы, коммутатор, накопитель результатов и последовательно соединенные сумматор, дешифратор пороговых значений и блок управления, подключенный к управляющим входам коммутатора, накопителя знаков и накопителя результатов, выход которого соединен с входом сумматора, к второму входу которого подключена схема сравнения, при этом буферные элементы подключены к коммутатору, выход которого соединен с сигнальным входом накопителя знаков и вторым входом схемы сравнения, а дешифратор пусковых комбинаций подключен к блоку управления, причем выход сумматора соединен с входом накопителя результатов.

Источник информации, принятый во внимание при экспертизе:

1. Гордон Ф. Г. и Нурмухаммедов Л. Х. О фазировании датчиков испытательных тестов. †«Вопросы радиоэлектроники», Сер. XI.

Вып. 6, 1965 (прототип).

556561

Составитель Е, Любимова

Техред 3. Тарасова

Редактор Н. Суханова

Коррсктор А. Николаева

Типография, пр. Сапунова, 2

Заказ 1119/13 Изд. № 410 Тираж 815 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 7К-35, Раушская наб., д. 4/5