Процессор

Иллюстрации

Показать всеРеферат

СП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 557366 (61) Дополнительное к авт. свих-ву (22) Заявлено08. 12. 74 (21) 2082196/24 с присоединением заявки %(23) Приоритет— (43) Опубликовано05.05.77.Бюллетень ¹ 17 (45) Дата опубликования описаиия09.07. 77 (51) M. Кл.т

СТ06 F15/OO

Гасударственный намнтет

Совета Инннстрвв СССР в денем нзабретеннй н отнрмтнй (53) УДК 681.325 (088,8

Р, И. Заславский, 5. П. Нефедченко, Д. Я. Стоенко, Л. И. Фиалко, В. H. Харитонов и A. П. Шередин (72) Л вторы изобретения

Киевский ордена Трудового Красного Знамени завод электронных вычислительных и управляюших машин (71) Заявитель (54 ) ПРО РЕССОР

Изобретение относится к вычислительной технике и может быть использовано при конструировании процессоров, оборудование которых используется для передачи данных между каналами ввода-вывода и главной па- 5 мятью, Известен процессор, содержаший информационные регистры и каналы, первые вьтходы и входы которых подключены соответственно к входным и выходным информацион- !Ю ным шинам главной памяти, а вторые выходы — к адресным шинам, которые через регистр адреса соединены с адресным входом главной памяти, информационные регистры соединены также двусторонней связью !5 с арифметическим блоком jl).

Недостатком этого устройства является значительный расход оборудования, связанный с наличием адресных шин, п также 20 аппаратуры для хранения и модификации адресов в каналах..

Наиболее близким техническим решением является процессор, содержашяй блок местной памяти, выход и вход которо1 о соедике- 25 ны соответственно с первыми входом и выходом информационного регистра, второй выход которого через .сумматор соединен с первым входом выходного регистра, первый выход которого соединен со вторым входом информационного регистра, вторые вход и выход выходного регистра соединены соот ветственно с первыми выходом и входом процессора, выходной регистр также соединен двусторонней связью с информационной магистралью каналов, второй выход сумматора соединен через последовательно соединенный узел формирования признаков, первую группу элементов И, регистр признаков с первым входом узла микропрограммного управления, второй вход которото соединен с единичным выходом первого триггера режима, единичный и нулевой входы которого соединены соответственно с первым и вторым выходами узла управл»ния микропрерываниями, вход которого соединен со вторым выходом процессора, у;и л управления микропрерываниями соединен двусторонней связью с узлом мякропрот.рпммного управления.

5. {" 36

НЕД0Ста КОМ Н" ГеС! . РГГ е: {е" "..f Ра чн-ляется потеря мал ннного B-,.: .. " на пере— ключение с; . -{{.,i. -„,{:,;!t -.е-:яя .;яаши.{ н:ых команд на режцм ввода-вывода и в обрагном направления. Эта потеря обусловлена 5, использованием местной пам.{ти для сохранения содержимого инфэрмационцого регис тра.

Целью изобретения является повышение быстродействия процессора за счет исклю» !О чения потерь машинного времени при переключении режимов.

Поставленная цель достигается тем, что устройство дополнительно содержит две группы элементов И, регистр хранения, два l5 элемента задержки и второй триггер ре кима, единичнь и я íyJ!BBotl аходы которого через элементы задержки соединены соответственно с первым и BTopbtM выхопамн узла управ- е:IHII м {Koo .:эерыааниями,. нуле- {{{ вой вход «терег триггера режима соединен с управляющим входом второй группы элементов И, а нулевой выход - с управляющими BKOHBIIH первой н третьей групп элементов И, трет - { выход н вход i{j фор- 2б мационыогo per mcòðà оединены через по{ {{{";{{р{: ; .w { {{,1 { а T{ со ° tt { . т; с . 7 р

Ь{{- .: Ь i ои l l; i ° t;iPim- {{{{и И BJJOPP iV групгу элементов И.

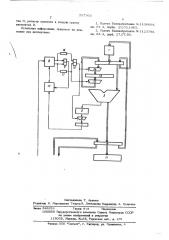

На чертеже изображена блэк-схема прэ- ЭО це{ .с{За ..

Процессор содержит блок 1 местной памяти, информацион-.гый регистр 2, суммат:.",. -. » я{не{{ регистр 4 узел 5 {for.мн-рования признаков, первая группа элементов И 6, регисчр 7 признаков, узел. 8 управления KIIIK omnetll I B,--: {{{п, { рн-г --о 9 n{» у;.е.г лення, содержаший память микрокоманд, регистр адреса, регистр микрокоманды с дешифратором мпкрооперац{ий{ информационная магистраль 11 каналов, вторая группа элементов И 12, регистр 13 хранения, третья группа элементов И 14, второй триггер режима i5, элементы 16,17 задержки.

Устройство работает следующим образом.

В режиме выполнения машинных команд (режим процессора) триггеры 9 и 15 находятся в нулевом состоянии, сигналы на их входах отсутстьуют. Из блока 1 информация считывается в информационные регистры 2 (на чертеже показан один из трех рет истров). Содержимое информационного регистра 2 передается на входы сумматора 3, результат операции которого помещается в регистр 4. Из последнего информация поступэ{ r в главную память процессора или (и) а один из информационных регистров 2. Из информационного регистра 2

4

0. а за;,нс -{лается в блок 1 или (и) переда «:, на Вход сумматора 3, В каждом цикле содержимое регис гра 2 переписывается в регистр 13. Передача осуществя{яется через третью группу элементов И 14, на управляющем входе «оторой действует разрешающий потенциал с нулевого выхода триггера 15. Этот же по тенциал поддерживает в открытом состоянии первую группу элементов И 6, через которуго признаки, формируемые узлом 5, передаются в регистр 7, I"rre они запоминаются, Содержимое регистра 7 служит условием ветвлений для микропрограмм процессора.

Одновременно с выполнением микропрограммы процессора происходит побайтная переда-{а данных между каналами ввода-вывода и внешними устройствами. Если выполняется операция чтения, данные принимаются из внешнего устройства и накапливаются в канале. Если выполняется операция записи, данные из канала передаются во внешнее устройство, Обмен данными между каяалами и внешними устройствами вы-{ {1тottOivtHo, без использования микропрограммного управления.

Ka trB B0 н{.кает необходимость в обращении к главной памяти, каналы вырабатывают запросы на микропрерывание, посту-.

rIaroIIIm{=. на вход узла 8. Последний выделя»-.,аиболее приоритетный из одновременно существующих запросов и вырабатывает последовательность сигналов, реализующую переключение на режим ввода-вывода.

Если запрос принят узлом 8 в цикле вь пелнения микрокоманды процессора с номе {, " ел:.дующем цикле выполнение микрокоманды >+ 1 совмещается с переключением на режим ввода-вывода: в узле

10 сохраняется адрес очередной микроко- манды процессора (A, +2), формируется адрег пеi. -ot . я{крекоманды ввода-вывода и с ттывается эта микрокоманда; триггер 9 устанавливается в единичное состояние.

Сягпая на единичном входе триггера 9, задержанный элементом 16, переключает и единичное состояние второй триггер 15, в результате чего запираются первая и трег1 я группг- элементов И 6 и 14 и тем самым запрещается запись и регистры 7 и

13. Задержка, формируемая элементом 16, подобрана таким образом, что триггер 15 устана{ лпаается B единичное состояние, этим ебее {{.чивается сохранение в perH рах 13 и 7 именно той информации, которая была с{ро1 миролана в регистре 2 и узJIe 5 B Kottg{. . цикла BBIIIoJIHBHHst MHKPoKo» манды Ъ +1 — последней микрокоманды процессора, выполнявшейся l!erleir микоопое5573 >g

Ь !

)б рыванием. (Элементы 16 и 17 могут быть реализованы, например, и виде сдвиговых регистров).

Вслед за микрокомандой процессора

Ъ +1 выполняется первая микрокоманда микропрограммы ввода-вывода. Эта микропрограмма осуществляет обращение к главной памяти дпя передачи данных в канал или иэ него. Адрес данных считывается из блока 1 и регистр 2 и затем передается в сумматор 3, где к нему прибавляется "4", если обмен с главной памятью четырехбайтовый. Обновленный адрес поступает в регистр 4, затем в регистр 2 н записывается в блок 1.

Он же с регистра 4 передается в главную память. По этому адресу происходит передача данных между главной памятью и каналом; если выполняется операция чтения, данные через информационную магистраль

11 каналов и регнстр 4 записываются в главную память. Если выполняется операция записи, данные считываются иэ грааной памяти и через регистр 4 и информационную магистраль ll передаются и канал.

На выполнение микропрограммы канала требуется W циклов. Если в цикле считывания микрокоманды тп отсутствуют запросы от каналов, ожидающие обслуживания, происходит возврат на микропрограмму процессора. Если микрокоманда ттт не использует регистр 2, цикл возврата совмещается с

85 циклом выполнения микрокоманды ттт. Во время этого цикла: в узле 10 считывается очередная микрокоманда процессора

{ т1 +2), а триггер 9 сбрасывается в нул евое состояние.

Сигнал на нулевом входе триггера 9, задержанный элементом 17, открывает вт рую группу элементов И 12, разрешая передачу в регистр 2 из регистра 13, и сбрасывает в нулевое состоянпе триттера

15. Величина задержки, формируемой элементом 17, подобрана такой, чтобы восстановление информации в регистре 2 сброс ЬО триггера 15 происходили на одном синхроимпульсе цикла выполнения госледней микрокоманды ввода-вывода. В результате к моменту возобновления работы микропрограммы процессора содержимое регистров

2,7 и состояние схем оказываются такими же, как если бы микропрерывзниа не было.

За цнклом выполнения тп -й микрокоман. ды ввода-вывода следует цикл выполнения (тт +2) -ой микрокоманди процессора, и Ьл таким образом возобновляется работа микропрограммы процессора.

Таким образом в предложенном процессоре переключение режимов совмещено Во времени с выполнением микрокоманд. Благодарк этому на каждое обращение к главной памяти со стороны каналов процессор затрачивает равно столько машинных циклов, сколько необходимо для вьптолнения микропрограммы ввода-вывода. В резуль тате на каждом таком обращении экономится два машинных цикла, что приводит к существенному повышению производительно".ти процессора.

Формула изобретения

Процессор, содержащий блок местной памяти, выход и вход которого соединены соо ветственио с первыми входом и выходом информационного регистра, второй выход которого через сумматор соединен с первым входом выходного регистра, первьгй выход которого соединен со вторым входом информацяонного регистра, вторые вход и выход выходного регистра соединены соответственно с первыми выходом и входом процессора, выходной регистр также соединен двусторонней связью с информационной магистралью каналов, второй выход сумматора соединен через последовательно соединенный узел формирования признаков, первую группу элементов И, регистр признаков с первым входом узла микропрограммного управления, второй вход которого соединен с единичным выходом первого триггера режима, единичный и нулевой входы которого соединены

c 0 o òÂå" отвеяно с пер вьГ 1 я BTDpbTM Выходя ми узла управления микропрерываниями, вход которого соединен со вторым выходом процессора, узел управления микропрерываниями соединен двусторонней связью с узлом микропрограммного управления, о т— л и ч s ю тй и и с я тем, что, с целью повышения быстродействия процессора, он дополнительно содержит две группы элементов И, регистр хранения, два элемента задержки и второй тритгер режима, единичный и нулевой входы которого через элементы задepжкн соединены соответственно с первым и вторым выходами узла управления микропрерываниями нулевой вход второго триггера режима соединен с управляющим входом второй группы эломентов И, а нулевой выход - с управляющимк входами первой и. третьей групп элеменТоВ И, третьи выход и вход информационного регистра сосдинены через последовательно соединенные третью группу элемен»

557366

Составитель Т. Арешев

Редактор И. Марховская ТехредА. Йемьянова Корректор А. фипенко

Заказ 848/59 Тираж 818. Подпис ное

11НИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113О35, Москва, Ж 35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

7 тов И, регистр хранения и вторую группу элементов И.

Источники информации, принятые во внимание при экспертизе:

1. Патент Великобритании N 1108804, кл. 64 А, опубл. 29.03.1965.

2. Патент Великобритании % 1123790, кл. 64 А, опуб, 27.07.66.