Устройство для квантования случайного процесса

Иллюстрации

Показать всеРеферат

О П И C -"A Н И Е

Союз Советских

Социалистических

Республик (» 557373

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 25.06, 75 (21) 2159050/24 с присоединением заявки №(23) Приоритет— (43) Опубликовано05.05 77,Бюллетень № 17 (45) Дата опубликования описания 09.07.77 (51) И. К .

006 F 15/36

Гасударственный комитет

Соввтв Министров СССР оо делам изобретений и открытий (53) УДК 681.325 (088.8) Г. Г. Живипов, Г. С, Певзнер, С, К. Турченкова и А. Б. Шадрин (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КВАНТОВАНИЯ СЛУЧАЙНОГО FIPOUFCCA

Изобретение относится к области вычислительной техники и может найти применение при анализе случайных процессов.

Известно устройство для квантования случаййого процесса, содержашее блок управления, аналого-цифровой преобразователь, блок сравнения, распределитель,.счетчики, дешифратор, блок усреднения, логические элементы (11, Недостатком этого устрой» ства является его сложность. 10

Наиболее близким техническим решением к данному изобретению является устройство дпя квантования случайного процесса, содержащее блок управления, блок вычитания, первый и второй входы которого соединены соответственно с выходами первого и второго аналоговых фиксаторов, первые входы которых являются входом устройства и соединены с первым входом аналого-цифрового преобразователя, выход которого является выходом устройства j2).

Недостатком этого устройства является низкая точность квантования случайного процесса. 25

Цепью изобретения является повышение точности. для достижения этой цепи в предложенное устройство введены блок усреднения, задатчик относительной ошибки, блок памяти и делитель частоты, .первый выход которого соединен с6 входом блока управления, второй выход — со вторым входом аналогоцифрового преобразователя, первый вход - с ттервым выходом блока усреднения, а второй вход — с первым выходом блока памяти, второй выход которого подключен к первому входу задатчика относительной ошибки, а третий выход - к первому входу блока усреднения, второй вход которого соединен с выходом блока вычитания, третий вход— с выходом задатчика относительной ошибки, а второй выход — с первым входом блока памяти, Выходы блока управления соединены с управляюшими входами блока вычитания, аналоговьк фиксаторов, блока усреднения, аналого-цифрового преобразователя, делителя частоты, задатчика относительной ошибки и блока памяти.

557373

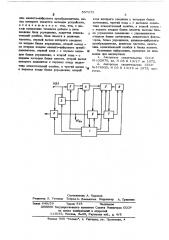

Е .:. х-схема устройства приведена на ч=:-„3Y же.

Устройство содержит блок управления 1, два аналоговых фиксатора 2,3, блок вычитания 4, блок усреднения 5, аналого.цифровой преобразователь 6, блок памяти 7, задатчик относительной ошибки 8 ы целитель частоты 9, 10

Измеряемый сигнал через аналоговые фиксаторы 3, 3 подается на блок вычитания 4, выход которого соединен с блоком усреднении модулей 5. На вход преобразователя 6 поступает измеряемый сигнал. 16

Входы блока усреднения модулей 5 соединены с выходами блока памяти 7 и управляемого задатчика 8. Выходы блока усреднения модулей 5 соединены с блоком памяти 7 и управляемым делителем частоты 9, 20 выход которото соединен с преобразователем 6. Вхоц эадатчика 8 соединен с выхо дом блока памяти 7.

Устройство работает следующим обрезом, 35

По командам с блока управления 1 в (tl+ 1)-ом цикле совместно фиксаторы 2, 3, блок вычитания 4, блок усреднения 5 и блок памяти 7. определяют 78 текущих оценок средних модулей jC(с ьW) j «30 по алгоритму

С (p Г) =С(,одф) +(м+ ) (AU(%+pat)Ои) (- с(Ф дг))

85 где С(,О ь )ц+ . C(P Ь ) и кушая и предыдущая оценки,О - и ордынаты средних модулей, хранимые в,0 -ом регыстре блока памяти 7 и выцаваемые в блок усреднения 5;

/u(+) î дг)- о(Ч/

-модуль текущей разности формируемый в блоке вычитания 4;

dt - начальный шаг по аргумеиту3 ,,а 3,Л,М =4,И,М- объем выборки.

Параллельно преобразователь 6 коцит- . рует случайный процесс 0 (4) на участке (,,yt„3, гце Ь4 .-ч и шаг по времени.

М

После N циклов в блоке памяти 7 опре. делены оценки средних модулей разности С (,о д Г) f и С(„), где Г„- интервал корреляции процесса .. О (Ф); Оценки С (,0 д Г ) связаны с приращением АКФ Ь Й (М А г ) по фор к муле C,(л дt) = 2ря 13(o)-ÿ(äüñ)= 2/1/м "4дя(,с д )

По командам с блока управления 1 иэ блока памяти 7 оценка С, (Г„) 60

4 считывается в задатчыке относительной ошибки 8, где формируется абсолютная ошибка аппроксимации Е = 9 ((<х) где S> — относительная приведенная ошибка аппроксимации, заданная априорно в эадатчике относительной ошибки 8.

Последовательность оценок j С (, д g) ) поступает ыз блока памяти 7 в блок усреднения 5, где формируются разности

j(. (дг)- 1, $z - поступает в блок усреднения д с задатчика относительной ошибки 8.

В момент, когда, например, при,М Ю выполнится в первый раз условие ((: (,о д|)-, ) > 0, с блока усреднения 5 в делитель частоты 9 подается сигнал фиксации коэффициента деления К < 5 + 1 6.

Формирование .К,„ в делителе частоты 9 осуществляется с ломощью счетчика, который подсчитывает число разностей (С(,одг)

-f.,) 0 до выполнения условия (С(и дт)- f ) > О . B соответствии с коеффициентом деления Ко автоматически изменяется время преобразования и шаг по времени hi÷ = ü4 K /тп -«д4 6/и -на чальньгй шаг по времени.

На выходе делителя частоты 9 формируются импульсы управления аналого-цифровым преобразователем 6 с периодом а 1,, который равен оптимальному шагу Ь, аппроксимации А КФ R (С д Г)

Поддержание 1ч д ч позволяет в предлагаемом устройстве повысить точность кодирования случайного процесса U (1 ) (эа счет автоматического уменьшения динамической ошибки в 3-4 раза, обусловлен- ной измененыем входного сигнала 0 (1 ) за время преобразования АФч ).

При достижении равенства,К ч = п с делителя частоты 9 в блок управления 1 выдается сигнал о прекращении увеличения времени преобразования < y в преобразр вателе 6, и с блока. управления 1 выдаеч ся команда в фиксатор 3 о включении его контура динамической памяти (для восста новления при больших задержках д ч 3

> Tn ц Г запомненного уровня исследуемого сигнала).

Формула изобретеныя

Устройство цля квантования случайного процесса, содержащее блок управления, блок вычитания, первый и второй входы ко горого соединены соответственно с выходами первого и второго аналоговых фиксаторов, первые входы которых являются вхОдом устройства ы соединены с первым вхо557373

Составитель А. Kapacos

Редактор Л. Утехина Техред.А. Демьянова Корректор А. Гриценко

Заказ 848/59 Тираж 818 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

11ЗОЗ5, Москва, Ж35, Раушская наб., д. 4/S

Филиал ППП "Патент, г, Ужгород, ул. Проектная, 4 дом аналого-цифрового преобразователя, выход которого является выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности работы в него введены блок усреднения, задатчик относи тельной ошибки, блок памяти и делитель частоты, первый выход которого соединен со входом блока управления,. второй выходсо вторым входом аналого-цифрового преоб разователя, первый вход - с первым выхо- 19 дом блока усреднения, а второй вход - с первым выходом блока памяти, второй выход которого подключен к первому входу задатчика относительной ошибки, а третий выход» к первому входу блока усреднения, второй вход которого соединен с выходом блока вычитания, третий вход - с выходом задач чика относительной ошибки, а второй выходс первым входом блока памяти; выходы блока управления соединены с управляющими входами блока вычитания, аналоговых фиксагоров, блока усреднения, аналого-цифрового преобразователя, делителя частоты, эадат чика относительной ошибки и блока памяти.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

¹ 432676, кл. Н 03 К 13/17 от 1972.

2. Авторское свидетельство СССР

¹474935; Н 03 К 13/16 от 1973, прототип.