Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву

Союз Советских

Социалистических

Республик (ll) S5743S (51) М. Ел е G 11 С 11/00 (22) Заявлено 28.01.7б (21) 2319925/24 с присоединением заявки № (23) Приоритет (43) ОпУбликовано 05.05:77. Бюллетень № 17 (53) УДК 681.327 (088.8) Государственный номитет

Совета Миииотров СИР по делам изобретений и открытии (45) Дата опублиновання описаннв 2406.77 (72) Авторы изобретения

В. И. Агафонов и В. С. Голубев (71) Заявитель (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устройствам. . Известны буферные запоминающие устройства.

Одно из известных устройств содержит адресный накапитель, датики кода адреса записи и 5 с впывання, блок формирования сигнала о заполнении накопителя, реверсввный счетчик f 1 j. Однако в этом устройстве из-за сбоя счетчика вырабатывается ложньй сигнал о заполнении накопителя, что приводит к искажению информации, вводимой в, 10 накопитель, или к преждевременной блокйровке. ввода информации, сокращающей эффективную емкость накопителя, Наиболее близким техническим решением к данному изобретеьшю является буферное заломи- 15 нающее устройство, содержащее реверсивный счетчик, выходы которого подключены к адресным входам накопителя, а входы -- сботввтственно к выходам генератора импульсов и блока модификации кода адреса, входы которого соединены с а шиной Считывание" и вькодом элемента НЕ (2).

Недостатком д нного устройства является надежная работа при передаче начальных и конечных блоков информащ и, хранящейся в накопителе, :характеризующаяся либо перестановкой переданных блоков информации (конечных на место начальных), либо размножением ошибки.

Такие искажения возникают всякий раз, когда

- число запрашиваемых блоков превьппает число переданных вначале блоков информации или число блоков служебной информации, влекующих после окончания передачи всех записанных в накопитель блоков информации.

Целью изобретения является повышение надежности устройства.

Для этого в устройство включены коммутатор и анализаторы .состояния счетчика, входы одного из анализаторов состояния счетчика подключены соответственно к вьгходам реверсивного счетчика и к шине "Запрос", входы другого анализатора состояния счелнка соединены соответственно с выходами реверсивного счетчика и выходом элемента НЕ, вход которого подключен к шине "Запрос", а выходы анализаторов состояния счетчика соединены со входом коммутатора, выход которого подключен к запрещающему входу! накопителя. °

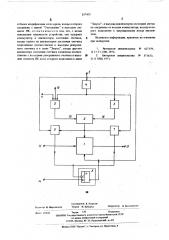

На чертеже показана блок-схема устройства, Устройство содержит накопитель 1, реверснвньп счетчик 2, вьшоЬняющий функции датчика кода адреса, генератор импульсов 3, элемент HE 4, 557415 блок модификации кода адреса 5, анализаторы начального 6 и конечного 7 состояний счетчика, ком. мутатор 8, шины "Запрос" 9, "Сннхроимпульсы" 10, "Считывание" 11, "ввод" 12, "вьвод" 13, "установка в "О" 14.

Входы анализатора 6 подключены соответственно к выходам счетчика 2 и к шине 9, входы анализатора 7 соединены соответственно с выходами счетчика 2 и выходом элемента НЕ 4, вход которого подключен к шине 9. Выходы анализаторов 6 и 7 соединены со входом коммутатора 8, выход которого подключен к запрещающему входу накопителя 1. Счетчик имеет входы "Сложение" 15 и "Вычитание" 16.

Устройство работает следующим образом.

11акопитель 1 заполняется информацией с первого по последний адрес. При наличии сигналов

"Считывание" и в случае отсутствия сигналов "Запрос" сигналы блока модификации кода адреса 5 в такт с сннхроимпульсами подаются,на вход "Сложение" 15 реверсивного счетчика 2, который вырабатывает код адреса числа, подлежащего выдаче в канал связи. Считанное с накопителя 1 н переданное в канал связи число перезапнсывается по выбранному адресу.

При поступлении сигнала "Запрос" прерывается подача сигналов на вход "Сложение" 15 реверсивного счетчика 2 и осуществляется эануск генератора импульсов 3. Количество импульсоВ, вьщаваемых генератором 3, может быть различным и в общем случае определяется числом запрашиваемых блоков информации, которое постоянно для установленной линии связи, При изменении кода ащзеса в реверсивном счетчике 2 нод действием импульсов, поступающих на вход "Вычитание" 16, Выборка в накопителе блокируется благодаря связи шины "Запрос" 9 с запрещающим входом накопителя 1.

Повторная передача информации начинается после снятия сигнала "Запрос".

Если сигнал "Запрос" поступил после переяячи

В канал связи трех блоков информации и %есло запрашиваемых блоков равно 5, то, нри поступлении сигнала "Запрос" блокируется адресный вход накопителя 1, разрешается работа анализатора начального состояния 6, и на вход "Вычитание" 16 реверсивного счетчика 2 поступают импульсы реверса. При прохождении реверсивного счетчика 2 через начальное состояние (после 3 импульсов ре. верса) на выходе анализатора 6 цоявляетея сигнал, который устанавливает коммутатор 8, например, счетный триггер, в состояние, нри котором на его выходе связанном с запрещающим входом накопи. теля.1, возникает сигнал, блокирующий выборку информации из накопителя 1 в течение действия последующих двух импульсов реверса.

При снятии сигнала "Запрос" анализатор 6 выключается, а работа анализатора 7 разрешается. Сигначы модификации кода адреса, поступая на вход

"Сложение" 15 реверсивного счетчика 2, будут иэменять код адреса в течение двух тактов без выдачи информации иэ накопителя 1, так как íà его запрещающий вход подается сигнал запрета с коммутатора 8. При переходе через конечное состояние реверсивного счетчика 2 на выходе анализатора 7 формируется сигнал, который поступает на вход коммутатора 8. На его выходе формируется сигнал, разрешавший считывание информации иэ накопителя 1.

1О При последующей смене кода адреса, начиная с адреса, соответствукнцего первому блоку информации, информация будет поступать на шину 13 запоминакнцегоустройства. Таким образом, в канал связи передаются только те блоки информации, !

Ь 1которые были переданы ранее.

Аналогично устройство работает и в случае, когда сигнал "Запрос" поступил после передачи последнего блока информации и следующих эа ним, например трех служебных блоков.

20 После считывания последнего блока информации анализатор 7 выдает сигнал, устанавливающий коммутатор 8 в состояние, при котором на его выходе формируется сигнал, запрещающий выборку информации из накопителя 1. При этом счет25 чик 2 продолжает изменять свое состояние под действием импульсов модификации кода адреса, поступавших на вход "Сложение" 15 в течение передачи служебных блоков. Таким образом, после

4 передачи трех служебных блоков код счетчика 2

30 будет соответствовать третьему адресу накопителя.

Прн поступлении сигнала "Запрос" разрешается работа анализатора 6, на эапрешаияций вход накопителя 1, поступает запрещающий имиульс, а на вход "Вычитание" 16 счетчика 2 поступают импульВВ сы, обеспечивающие реверс счетчика 2 на пять тактов.

При прохождении реверсивного счетчика 2 через начальное состояние (после трех импульсов реверса) на выходе анализатора 6 формируется сиг40 нал, который устанавливает коммутатор 8 в состояwe, при котором с его выхода снимается сигнал запрета .выборки информации из накопителя. В последуюшие два такта реверса счетчика 2 выборка информации из накопителя блокируется. сигналом

45 "Запрос, поступающим на запрещающий вход накопи геля 1.

При снятии сигнала "Запрос" считывание информации из накопителя 1 начинается с последнего адреса.

50 Таким образом, в канал связи будут переданы только запрещенные блоки информации, что обеспечивает достоверность переданного сообщения.

Формула изобретения

Буферное запоминающее устройство, содержашее реверсивный счетчик, выходы которого подключены к адресным входам накопителя, а входы соответственно к выходам генератора импульсов

557415

Составитель В. Рудаков

Техред Н. Бабурка Корректор 33. Веселовская

Рслакзор М. Марковская

Тираж 7 29 Подписное

ННИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская иаб., д. 4/5

Заказ 854/61

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 и блока модификации кода адреса, входы которого соединены с шиной Т п1тывание" и выходом элемента НЕ, отличающееся тем, что, с целью повышения надежности устройства, оно содержит коммутатор и анализаторы состояния счетчика, входы одного иэ анализаторов состояния счетчика подключены соответственно к выходам реверсивного счетчика и к шине "Запрос", входы другого анализатора состояния счетчика соединены соответственно с выходами реверсивного счетчика и выходом элемента НЕ, вход которого подключен к шине

"Запрос", а выходы анализаторов состояния счетчика соединены со входом коммутатора, выход которого подключен к запрещающему входу накопителя.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство !! 427379, G 11 С 11 00, 1973.

lO 2, Авторское свидетельство !! 37!613, G 1! 9 00, 197! .