Устройство для передачи информации с адаптивной дискретизацией

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВйдЕТИЛЬСТВ (61) Дополнительное к авт. свид-ву— (22) Заявлено 24.06.74 (21) 2036038/09 с присоединением заявки ¹ 2036037/09 (23) Приоритет— (43) Опубликовано 0S.05.77. Бюллетень № 17 (45) Дата опубликования описания 0S.08.77

Союз Советских

Социалистических

Республик (11) 557485 (51) M. KJt.o

Н 03 К 13/00

Н 04 L 3(00

Государственный комитет

Соввтв Министров СССР по деяам изобретений и открытий (53} УДК

621.394.14 (088.8) В, А. Скрипко, Г. 3. Сергеев, Л. Е. Софинский и В. И, Серов (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ

С АДАПТИВНОЙ ДИСКРЕТИЗАЦИЕЙ

Изобретение относится к технике связи, может использоваться в аппаратуре передачи данных.

Известны устройства для передачи информации с ад аптивной дис кретизацией.

Известно устройство для передачи информации с адаптивной дискретизацией, содержащее сдвигающий регистр в виде последовательно соединенных ячеек памяти, элементы И, ИЛИ, триггеры и тактирующий блок. Дискретная информация, поступающая на вход сдвигающего регистра, разделяется на два потока — прямой и инверсный, задерживается и сравнивается с предшествующим зн ачением.

Известно также устройство для передачи информации с ад BIITHBHoH дискретизацией, содержащее коммутатор, преобразователь аналог-код, логический узел, блок формирования оценочных значений сигнала, блоки памяти, выходные регистры, элементы ИЛИ, НЕТ и тактирующий блок. Однако такое устройство не обладает достаточно высоким быстродействием, что затрудняет его применение при перед аче быстроменяющихся процессов.

Наиболее близко к предлагаемому устройство для передачи информации с адаптивной дискретиза. цией, содержащее коммутатор, соединенный с преобразователем аналог-код, под ключенным через последовательно соединенные логический узел и блок формирования оценочных значений к блоку памяти и регистру кода, а также собирающий блок, причем соответствующие входы логического узла, блока

5 формирования оценочных значений и блока памяти соединены с тактирующим блоком.

Наиболее сушественный недостаток такого устройства — недостаточное быстродействие.

Цель изобретения — повышение быстродейст10 вия, Для достижения этой цели в устройстве для передачи информации с адаптивной дискретизацией, содержащем коммутатор, соединенный с преобразователем аналог-код,.подключенным через после15 довательно соединенные логический узел и блок формирования оценочных значений к блоку памяти и регистру кода, а также собирающий блок, причем соответствующие входы логического узла. блока формирования оценочных значений и блока памяти соединены с тактирующим блоком, преобразователь аналог-код выполнен в виде блока сравнения с п-квантованными выходами, логический узел выполнен в виде и параллельно включенных цепей, каждая иэ которых состоит из последов ательно

25 соединенных элементов ИЛИ и НЕТ, а блок форми557485 рования оцено лых значений выполнен в вцде Il — 1 параллельно включенных цепей, каждая из которых состоит из последовательно соединенных ячейки памяти и вентиля, при этом квантованные выходы

1 преобразователя аналог-код подключены к первым входам элементов ИЛИ, вторые входы которых соединены с соответствующими выходами блока памяти, а вход запрета oro элемента НЕТ соединен с соответствующими квжтованньтми выход ами преобразователя аналог- код, которые через собирающий блок подключены ко входу запрета нулевого элемента НЕТ, выход которого через ячейку памяти подключен к соответствующему входу блока памяти, лричем выход нулевого элемента НЕТ соединен с управляющими входами первого и последнего вентилей через дополнительные элементы ИЛИ, а с управляющими входами остальных вентилей непосредственно; при этом вторые входы дополнительных элементов ИЛИ соединены с выходами соответствующих элементов НЕТ, Такое устройство для передачи информациис адаптивной дискретизацией обеспечивает повышение быстродействия при более глубокой адаптации и позволяет усреднить поток существенных выборок.

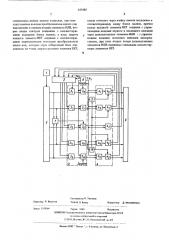

На чертеже приведена структурная электрическая схема устройства.

Коммутатор 1 соединен с преобразователем аналог-код 2, подключенным через последовательно соединенные логический узел 3 и блок формирования оценочных значений4 к блоку памяти 5 и регистру кодаб, а также собирающий блок 7, причем соответствующие входы логического узла 3, блока формирования оценочных значений 4 и блок памяти 5 соединены с тактирующим блоком 8; преобразователь аналог-код 2 выполнен в виде блока сравнения с и квантованными выходами, логический узел 3 — в виде и параллельно включенных целей, каждая из которых состоит из последовательно соединенных элементов ИЛИ 3, — 3, и элементов ПИ 3„. — 3, „соответственно, а блок формирования оценочных значений4 выполнен в виде и- 1 араллельно включенных цепей, каждая из которых состоит из последовательно соединенных ячейки памяти 4, — 4, и вентиля 4, — 4, соответственно. При этом квантованные выходы преобразователя аналог-код 2 подключены к первым входам элементов ИЛИ 3, — 3,, вторые входы которых соединены с соответствующими выходами блока памяти 5, а вход з ятрета каждого элемента HET

3Ä Ä 3,, 3,, 3,, соединен с соответствующими квантованными выход ами преобразователя аналог-код 2, которые через собирающий блок 7 подключены ко входу запрета нулевого элемента НЕТ 3„ выход которого через ячейку памяти 4, подключен к соответствующему входу блока памяти 5, причем выход нулевого элемента НЕТ 3, соединен с управляющими входами первого 4, и последнего 4, вентилей через дополнительные элеменгы ИЛИ 9 и

10, а с управляющими входами остальных вентилей тО

4, — 4, —; приэтомвторыевходы дополнительных элементов ИЛИ 9 и 10 соединены с выходами соответствующих элеменгов НЕТ 3, и За. работает устройство следующим образом.

Кагпл. параметр достигает оппре :, щого кван. тованного уровня, на входах элементов ИЛИ 3, и

3, появляются сигналы, которые в дальнейшем поступают на входы элементов НЕТ 3, и 3, соответственно. Одновременно сигнал через блок 7 по15 с

29

60 ступает на вход запрета элемента НЕТ З„и поэтому с приходом сигнала ТИ, сигнал появляется только на выходе элемента ИЛИ 3,, записывается в ячейку 4, и, пройдя через элемент ИЛИ 9 навентиль 4,, переключает его. С приходом сигнала ТИ, сигнал из ячейки 4, через вентиль 4, поступает в блок памяти 5, где записывается в виде единичного символа.

Поэтому для следующего цикла измерения в блоке 5 хранится код "00010". В следующем такте измерения сигнал ТИ, из блока 8 считывает из блока памяти 5 код "00010" и единичный символ, который через элемент ИЛИ 3, поступает в элемент

НЕТ 3 т, Одновременно ко входу блока 2 подключается измеряемый параметр.

В работе устройства возможны случаи, когда параметр не изменяется. Тогда выборка признается несущественной и в канал связи не переджтся, а в блок памяти 5 снова записывается код "00010".

Если параметр возрастает и достигает старшего квангованного уровня, выборка признается также несущественной, в канал связи не передается, а в блок 5 записывается код "00001 *.

Если параметр достигает младшего квантованного уровня, такая выборка считается существенной, передается в канал связи, а в блок 5 записывается код "00100".

Когда параметр достигает следующего кванто ванного уровня, в преобразователе аналог-код 2 с помощью коммутатора 1 появляются сигнапы, которые через элементы ИЛИ 3, — 3, поступают на элементы НЕТ 3, — За При этом с данного квантованного выхода сигнал поступает навход запрета элемента НЕТ 3, и через собирающий блок 7 — на элемент НЕТ 3,. Поэтому с приходом сигнала ТИ, только на выходе элемента НЕТ 3, . появляется сигнал, который записывается в ячейку 4,, à с прих

1 дом сигнала ТИ, переписывается через вентиль 4, в блок памяти 5. В этом случае в блоке 5 для следующего цикла измерения хранится код "00001".

В очередном такте измерения с приходом сигнал ла ТИ, с блока памяти5 через элемент ИЛИ 3, сигнал поступает на элеменг НЕТ 3, . Если параметр уменьшился и достиг другого квантованного уровня, сигналы начинают поступать на элементы НЕТ 3, и 3,,черезэлементы ИЛИ 3,иЗ, и на вход запрета элемента НЕТ 3, через собирающий блок 7. Поэтому с приходом сигнала ТИ, на выходах элеменгов НЕТ 3, и 3, появляются сигналы, которые записываются в ячейки4, и 4,. Кроме того, с элемента НЕТЗ, сигнал через элемент

557485

Ъ

35

И!1И ч поступает на управляющий вход вентиля 4,.

По: »)Mv ныход ячейки 4, соединяется со считы. нающим входом регистра 6, При этом вентиль 4, ос атется н исходном состоянии, при котором выход ячейки 4. через ячейку 4, соединяется с определенным разрядом блока памяти 5. Поэтому с приходом сигнала ТИ, сигнал ячейки памяти 4, ïîñòóïaет на регистр б, а в канал связи поступает первая выборка -- код, соответствующий этому квантованному уровню. Сигнал с ячейки 4, попадает на вход соответствующего разряда блока памяти 5, где для следующего цикла измерения хранится код

"00010". С приходом сигнала ТИ, код считывается из блока5, а в элемент HET3, через элемент

ИЛИ 3, затисывается сигнал. .Если параметр уменьшился и достиг более низкого квантованного выхода, сигнал появляется на соответствующем выходе блока 2 и через элемент

ИЛИ 3, поступает на злеменг НЕТ 3,. Поэтому с приходом сигнала ТИ, сигналы появляются на выходе злементов НЕТ Зт и аа и записываютсяв ячейки памяти 4, и 4,. Одновременно сигнал с элемента НЕТ 3, поступает на вентили 4, — 4,, которые подключаются через ячейки 4,, 4,, 4,, 4, к соответствующим входам считывания регистра кода 6.

С приходом сигнала ТИ, навыходах ячеек4, и

4, появляются сигналы. При этом из ячейки 4, сигнал поступает через вентиль 4, на регистр кода 6, а н канал связи передается код, соответствующий этому квангованному уровню, т. е. происходит вторая существенная выборка. При этом единичный код с ячейки 4, записывается в соответствующий разряд, а в блоке памяти 5 хранится код "00100". С приходом сигнала ТИ., единичный код с блока памяти 5 иосгуиает в ячейку памяти 4, Если парамегр достиг еще бонне гпгзкого квантованного уровня, иа соотнетствующил выходах преобразователя аналог-код 2 ио))нлянггся сигнаиь)> которые через .)пеменгы ИЛИ 3, и 1, записываются в элементы НЕТ З„и 3„. Одионремеино с блока 2 через собирнннций блок 7 сигнал иос) уг) ает на вход запрета энеме)пн НЕ 1 3,. !1озтому с приходом сигнала

ТИ) сигнал ионнпяегся го?)ько на выходе элемента IIET З„и заиисыннегся н ячейку памяти 4, > а также через знемгпгг HJIH 3, „пос)уиаег ианентиль

4, и перекнн)чае) его. l!ри з)ом сигнал ГИ, переписыннег )то) сиги;а из ячейки ? IQM)ttH 4, через вентиль 4Ä 8 соотнетсtâókt)ùtté разряд бпока иамяги 5, который храпи) коп "01000". Сигналом ТИ, код счип )ннегся и записывается н знеменг НЕТ 3,.

Если параметр возрос ио абсолютной величине и ности) друтог0 кнннтонаииого уровня, го сигналы

ТИ., и ГИ., заиисынакн н блок 5 код "10000", а ныборка иризи ветен несу) цествеиной.

Очередной сигнан ТИ,:читынает код из блока

ttat)tktти 5. tt н зпеме)п Н1".Г 3, „через элемент

ИЛИ 3, запись)нн "teн сигнал с соответствующего разр)гца. Еспи абсоп«л иня неничииа параметра умень)иип ась и цос гигпа цругого KBBktt îâaííîãî уровня, сигнал отсюда через элемент ИЛИ 3, поступает на элемеш НЕТ 3. и через собирающий блок на вход запрета )пеменга HET 3,; С приходом сигнала ТИ, на выходах элементов НЕТ:„и 3, „ появляются сигналы, поступающие в ячейки памяти 4. и 4,. Кроме того, сигнал с элемента НЕТ 3, через элем ггт ИЛИ 10 поступает на управляюгций вход вентиля 4,. При этом выход ячейки 4, соединяется со считывающим входом регистра кодаб.

Выход ячейки4„через вентиль 4,, находящийся в исходном состоянии, соединяется с соответствующим разрядом блока памяти 5. С приходом сигнала

ТИ, на выходах ячеек 4, и 4„появляются сигналы, один из которых поступает с ячейки 4, через вентиль4, на регистр 6, а в канал связи попадает третья существенная выборка — код, соот вет ству ющий этому квантованному уровню. Другой сигнал с ячейки 4„поступает через вентиль 4, в соответствующий разряд блока 5, в котором для следующего измерения хранится код "01000", который считывается сигналом ТИ, в элемент НЕТ 3, Если в этом случае параметр достигает другого квантованного выхода, сигналы записываются в элементы НЕТ З„и 3Ä. Поэтому сигнал ТИ., переписывает их в ячейки 4, и 4,. При этом сигнал НЕТ с элемента 3, поступает на вентиль 4„и переключает его. Сигнал с ячейки 4„через вентиль 4, поступает на регистр 6, и в канал связи выдается код, соответствующий этому квантованному уровню-четвертая существенная выборка, а сигнал с ячейки 4, поступает в соответствующий разряд блока 5, в котором хранится коц "00100 .

1 аким образом, устройсгво обеспечивает адаптивную выборку заданных квантонанных уровней на нисходящей ветви копебатенын?го процесса.

Форму?га изобретения

Устройство дпя передачи информации с адаптивной дискретизацией. содержащее комму) втор, соединенный с преоб1?азг?н))епел) a«a?tuk -код, и последовательно соецииенные ионический узел и блок формирования оценочнг)х значений. k)k>khoitbl которого лодкин)чеиы ко входил) t)!k<?Ka памяти и регистра коца, а также собирнюпгий блок, причем соотнетстнунндие нхоцы логического узна. бпока формиронания оценочных значений и блока памяти соединены с тактируницим блоком. î I и и ч а ющ е е с я тем, что.. цепьн;,))?нии)е)гия бысгродействия. преобразоназе ь нн;н)г)г-код выполнен н виде блока сравнения о «нацгонанными ныхода ми> логический узел ны) <яи«и в вице о иарапненьио включенных цепей, каждан it? которых лн:1о)г? из последонатспьно соепиненныл )пеменгг)н И.>1И и НЕТ, а блок форми1)онания;иви«)чных и)ачений выполнен в виде(о-1) инрн?гп !Ihkt» k)K)ikk?Nektkkbt) цепей, каждая из когорыл сос)оиз из иос?нпц)инге?) kt ) 557485

Лирет) Составитель О. Тихонов

Техред 3. Фанта

Редактор Б. Федотов

Корректор Д. Мельниченко

Закаэ 1109/64

Тираж 1065 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП " Патент ", r. У жгород, ул. Проектная, 4 соединенных ячейки памяти и вентиля, при этом квант ованные выходы преобразов ат еля аналог- код подключены к первым входам элементов ИЛИ, вторые входы которых соединены с соответствующими выходами блока памяти, а вход запрета каждого элемента НЕТ соединен с соответствующими квантов ан ыми выходами преобразователя аналог-код, которые через собирающий блок подключены ко ходу запрета нулевого элемента НЕТ, выход которого через ячейку памяти подключен к соответствующему входу блока памяти, причем выход нулевого элемента НЕТ соединен с управляющими входами первого и последнего вентилей через дополнительные элементы ИЛИ. л с управляющими входами остальных вентилей непосредственно, при этом вторые входы дополнительных элементов ИЛИ соединены с выходами соответствующих элементов НЕТ.