Устройство измерения качества каналов передачи дискретной информации

Иллюстрации

Показать всеРеферат

1": ;:Ь/е,,... аг - -e,и

4 " --@я4к

-Ф Флнет»»а мБр /

Союз Советскнх

Соцналнстнческнх республнк (11) -, 7ДС) (> (61) Дополнительное к авт. свил-ву— (22) Заявлено 16.09.74 (21) 2060636/09 с присоединением заявки № (23) Приоритет (бт) М y,„, о

Р 041 1/10

Н 04 1 11/08

Государственный номнтет

Совета Мнннстров СССР на делам изобретений

Н OTIIPblTIIII (43) Опубликовано 05.05.77. Бюллетень №17 д) удит.

621.394.61 (088.8) (45) Дата опубликования описания 05.08.77 (72) Авторы изобретения

В. Ф. Кисоржевский, Г. В. Писарев н С. А, Козловский (71) Заявитель (54) УСТРОЙСТВО ИЗМЕРЕНИЯ КАЧЕСТВА КАНАЛОВ

ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ

Изобретение относится к технике связи и может быть использовано для измерения отношения сигнад, помеха в каналах частотного радиотелеграфироваиия.

Известно устройство для измерения качества каналов, предназначенных для передачи дисюетной информации без применения при этом тестовых сигналов, и содержащее сумматор, входы которого соединены с частотным демодулятором 11). Выход сумматора через разделительную цепь подключен к первому квадратичному детектору и к одному из входов блока вычитания. Второй вход блока вычитания соединен с выходом указанной разделительной цепи, а выход подключен ко второму квадратичному детектору. Выходы обоих квадратичных детекторов соединены со входами делителя, На вход устройства поджтся смесь сигнала и алдитивной помехи. При этом напряжение на выходе дели. теля представляет собой функцию отношения мощностей сигнала и флюктуационной помехи и характеризует качество канала связи.

Если в канале наряду с флюктуационной действует также и сосредоточенная помеха, последняя воспринимается устройством как увеличение мощноспг полезного сигнала, и точность оценки качест ва канала падает.

Цель изобретения — повышение точности измерения отношения сигнал/помеха в условиях воздействия сосредоточенных помех.

Поставленная цель достигается введением вход ного интегратора. вход которого соединен со вха» дом устройства измерения качества каналов, первого и второго распределительных ключей, входы кото1О х соединены с выходом входного интегратора, -IepaoI o и второго основных интеграторов, входы которых соединены соответственно с выходами первого и второго распределительных ключей, первого и второго ключей считывания, входы которых соединены соответственно с выходами первого и второго основных интеграторов, а выходы — co входами делителя, а также введением блока фор. мирования управляющих импульсов, вход которого соединен со входом устройства измерения ка. щ RGTII> KBHRJloB, BblxoJI TBKToBblx нмпУльсов, Bhtxog импульсов смены значащих позиций входного сигнала с "единицы" на нуль" и выход импульсов смены значащих позиций входного сигнала с нуля" на "единицу" подклгочсны соответственно к управляющим входам входногп шпе1цаг< ра. первого и

557496 в i орого распределитель»ых ключей; а выход импульсов считыва»ия результата интегрирования соединен с управляющими входами обоих ключеи с читы вани я.

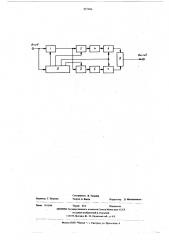

На чертеже изображена блок-схема предлагаемого устройства измерения качества каналов передачи дискретной и»формации.

Схема включает входной интегратор 1, первый 2 и второй 3 распределительные ключи, которые но сш »адам, поступающим на их управляюгцие входы, производят распределение выходных сигналов интегратора 1 по основным интеграторам 4 и 5. Последние осуществляют интегрирование поступающих на их входы сигналов за весь период измерения.

Схема включает.:"àê;æ"å первый 6 и второй 7 ключи считывания, через которые в конце периода измерения полученные результаты с и»теграторов 4 и 5 подводятся к входам делителя 8, определяющего отношение величин, подводимых к его входам напряжений, и блок 9 формирования управляющих импульсов, при помощи которого из входного сигнала вырабатыванпся импульсы, необходимые для управления работой входного интегратора и ключей.

Устройство измерения качества каналов работает следующим образом, На входной интегратор 1 и блок 9 формирования управляющих импульсов подается напряжение с выхода демодулятора, которое равно сумме напряжений сигнала и помехи при приеме, например, позиции "1", и только напрюкению помехи при приеме позиции "0". Входной интегратор "àêòîâûì импульсом с блока формирования 9 включается при приеме каждого единичного элемента сигнала.

Результаты интегрирования со входного интегратора подаются»а основные интеграторы 4 и 5 через распределительные ключи 2 и 3, которые работают попеременно гри каждой смене позиций принимаемого сигнала. Если, например, на ключ 2 отпирающий импульс с блока формирования9 подается при каждой смене позиции "1" и "0", то на ключ 3 отпирающий импульс поцается при каждой смене "О" и "1". Благодаря такому порядку работы распределительных ключей на основной интегратор 4 поступают толькб реэультатгя интегрирования суммы напряжений сигнала и помехи, а па основной интегратор 5 — только результаты интегрирования напряжении помехи.

Кроме того, если на вход измерителя поступает подряд несколько однозначных посылок, то на основные интеграторы подается только одна из них, а именно та, которая непосредственно предшествует смене позиций, В конце периода усреднения па ключи считывания 6 и 7 с блока формирования 9 подается импульс считывания, и са папы, накопленные в интеграторах 4 и 5, поступают на входы делителя 8. Величина напряжения на выходе делителя определяется выражением:

0ы ñ

+1

Ош Цд где V — выходное напряжение делителя;

Ос,0ш — усреднение значения напряжений сигнала и помехи;

Ос + Цш — усредненное значение суммы напряжений сигнала и помехи.

Нреимущества описанного устройства перед устройством, выбранным за прототип, заключаются з том, что сосредоточенная помеха попадает одновременно на оба основных интегратора, что обеспе. чивает повышение точности измерений отношения сьи ал/помеха.

2Р

Формула изобретения

Устройство измерения качества каналов передачи дискретной информации, содержащее делитель, выход которого является выходом измерителя, отл и ч ающ ее с я тем,что, с целью повышения точности измерения отношения сигнал/помеха в условиях воздействия сосредоточенных помех, в него введены входной интегратор, вход которого соединен со входом устройства измерения качества каналов, первый и второй распределительные клв- чи, входы которых соединечы с выходом входного интегратора, первый и второй основные интеграторы, входы которых соединены соответственно с выходами первого и второго распределительных, ключей, первый и второй ключи считывания, входьг которых соединены соответственно с выходки первого и второго основных интеграторов, а выхо ды — со входами упомянутого делителя, и блок формирования управляющих импульсов, вход которого соединен со входом устройства измерения качества каналов, выход тактовых импульсов, вы. ход импульсов смены значащих позиций входного сигнала с "единицы" на "нуль", выход имйульсов смены значащих позиций входного сигнала с "нуля" на "единицу" подключены соответственно к управляющим входам входного интегратора, первого н второго распределительных ключей, а выход им пульсов считывания результата интегрирования со. единен с управляющими входами обоих ключей считывания.

Источники информации, принятые во впиманиа при экспертизе:

1. Авторское свидетельство СССР М 339008, H 04 L 1/1О, 09.07.70.

557496

Составитель В. Телегин

Техред 3. Фанта

Редактор Г. Петрова корректор Я. Мельниченко Тираж. 815 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Заказ lllO/64

Филиал ППП Патент ", r. Ужгород, ул. Проектная, 4