Устройство цикловой синхронизации для блочных кодов

Иллюстрации

Показать всеРеферат

ОП ИКАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 55749 ) (61) Дополнительное к авт. свид-ву (22) Зал нлено 31.03.75 (21) "11859()j0() е п(эисоедннепием Заявки № (2>.э) 111) н о1) и гет (43) ()публиконано 05.05.77. Бюллетень № 17 (451 .1,(зта опубликования описания 05.08.77 (Ы) М. Кл.

l l 04 L 7/О ъ

Го удирствеиный иамите) Гвветв Министр()в СССР ев дегвм изовретеиии и вткри(тий (" () УДк () ) 1.3()4.(>() ((1>().(() И. Ф. Хомич (72) Лls!ÎÐ изобретения

Пензенский з((вод-ВГУЗ при заводе ВЭМ, фи»иал Пензенского политехнического инсгигу I a (71) Злят>нтель (S4) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

ДЛЯ БЛОЧНЫХ КОДОВ

Изобретение относится к технике передачи дискретной информации и может ист(оньзоваться в системах передачи данных блочными кодами.

Известно устройство цикловой синхронизации для блочных кодов, содержащее на »ередан>шей стороне последовательно соединенные кодирующий блок, к управляющему входу которого нодк»м>чен распределитель, и сумматор по моду»н> два, а на приемной стороне -- последователы<о соснине(нные входной регистр сдвига, выходы которого подключены к блоку вычисления проверок кода, сумматор

IIo модулю два и декодирующий блок, к унравлян>щему входу которого подключен выход генератора тактовых импульсов через делитель частоты, а также дешифратор (1).

Однако в обгцем случае передачи информации, закодированной блочным (п,к) кодом, известное устройство недостаточно заи(ищено на ряде несинхронных позиций от ножной синхронизации, вызванной статичностью передаваемой информации.

Цель изобретения -- уменьшение вероятности ложной синхронизации.

Для этого в устройство пик»оной синхронизации для блочных кодон, сод«ржап(ее на передан>п(ей стороне последовательно соединенные к()пиру«>(ций блок, к управляк»цему входу которого подключен распределитель, и сумматор tt(> модулю два, а на приемной с ) прон« -- нос»вдова те»ьно соединенные входной р(;ги«(р сдвига, выход>и которого цодкню5 (ictst>I к блоку вь)числ«ния проверок кода, сумматор

tI(> моду)но дви и д«кодиру)опп(й(блок, к управляющ«му висну ко(орого подкнн>ч и выход геператора

TBKI(>8>Ix H((III)»heов через д »Itte»I гас>огы, а также дешифратор, введены на передан»цей стороне

1p I)()(.»e)I()!seIe»»!«) e(>e)(HI(«I(IIII«ана»изап)р проверок к од а, 3» e > s e HI 3 а) le 1) )K K H и к» к) и, а I I (I ) нри « мн ой ст ороне I(((Ko(II(r«»I проверок кона, зл«м«)п НЕТ, ключ и донолнитеньныс сумматоры по модулю два, при этом на пере) гакнцей стороне второй выход

15 распредели(еля через кнк>ч нодклн>чен ко второму входу сумматора по модулю дна, выход которого подключен ко входу анализатора проверок кода, и на приемной стороне выходы блока нь(числения проверок кода полк»к)чень(ко вхо)гам соотнет. х0 ствуюн(их доно»ките!Ihtt(>lx сумматоров по модулю два непосредственно и через нак(нппе»), проверок кода, выход K0t()1)0(о II()!I K»н> (II K() в(()рому входуу сумматора по м()ду)п() два (с(н (»((«. к уцравлян>щему Rx()ft) которсч () п()чк:(к>ч(н вь(,о;(, )(е(пиг5 фратора, K()l()1)II)1I нонн>н(>чек к унр(ll(;l>ll ш«му вхо) 557499.и элсмегп а НИ . «ключенного между выходом c èåðçTîðà тактовых импульсов и входом делителя час готы.

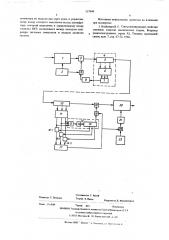

На чертеже изображена блок-схема предложенного устройства.

Устройство цикловой синхронизации для блочных кодов содержит на передающей стороне последовательно соединенные кодирующий блок 1, к управляющему входу которого подключен распределитель 2, и сумматор по модулю два 3, анализатор проверок кода 4 состоящий, например, из регистра сдвига 5, узла вычисления проверок кода 6 и дешифратора 7, элеменг задержки 8 и ключ 9, а на приемной стороне — входной регистр сдвига 10, выходы которого подключены к блоку вычисления проверок кода 11, накопитель проверок кода 12, состоящий, например, из элемента ИЛИ 13, элемента HE 14 и регистра сдвига 15, дополнительные сумматоры по модулю два 16, например, 16-1, 16-2, 16-3, дешифратор 17, ключ 18, сумматор по модулю два 19, декодирующий блок 20, делитель частоты 21, элемент НЕТ 22 и генератор тактовых импульсов 23.

На передающей стороне кодирующий блок 1, сумматор по модулю два 3, анализатор проверок кода 4, элемент задержки 8 и ключ 9 соединены последовательно, а второй выход распределителя 2 через ключ 9 подключен ко второму входу сумматора по модулю два 3.

На приемной стороне входной регистр сдвига 10, сумматор по модулю два 19 и декодирующий блок 20 включены последовательно. Выходы входного регистра сдвига 10 подключены также к блоку вычисления проверок кода 11, выходы которого подключены ко входам соответствующих дополнительных сумматоров по модулю два 16 (например, 16-1, 16-2, 16-3) непосредственно и через накопитель проверок кода 12, выход которого соединен со вторым входом сумматора по модулю два 19 через ключ 18, к управляющему входу которого подключен выход дешифратора 17. Выход дешифратора 17 соединен также с управляющим входом элемента

НЕТ 22, включенного между выходом генератора тактовых импульсов 23 и входом делителя частоты 21. К управляющему входу декодирующего блока 20 подключен выход делителя частоты 21, соединенного через элемент НЕТ 22 с генератором тактовых импульсов 23, Предложенное устройство работает следующим образом.

На передаче информация кодируется группо. вым (п,к) кодом в кодирующем блоке 1, который управляется распределителем 2 и постутгает через сумматор по модулю два 3 в анализатор проверок кода 4 для несинхронных сдвигов. Анализатор проверок кода 4 содержит п-разрядный регистр сдвига 5, соединенный с узлом вычисления проверок кода 6 и дешифратором 7. Последний вырабатывает единичный сигнал, если на выбр" ííûõ несинхронных сдвигах будет удовлетворяться закон построе35

5

29

30 ния (п,K) кода. Тогда этот сигнал поступал через элемент задержки 8 и открытый ключ 9 на умматор по модулю два 3, где складывается с проверочным знаком последующей кодовой комбинации.

Таким образом, в канал связи будут передаваться кодовые комбинации, которые дополнительно несут информацию о проверке выбранных несинхронньц сдвигов.

На приеме закодированная последовательность накапливается во входном регистре сдвига 10 и проверяется в блоке вычисления проверок кода 11 с каждым сдвигом. Результаты проверок на выбранных несинхронных сдвигах поступают в накопитель проверок кода 1 и затем сравниваются на дополнительных сумматорах по модулю два 16-1, 16-2, 16-3 со значениями проверок последующей кодовой комбинации. Таким образом, на синхронном сдвиге на входе дешифратора 17 будет (п-к) нулей и запрещающий сигнал на элемент НЕТ 22 не поступит, Поэтому генератор тактовых импульсов 23 в этом случае не изменит цикловой фазы делителя частоты 21, управляющего работой декодирующего блока 20 корректирующего кода. Для исключения поступления на вход декодирующего блока, 20 кодовых комбинаций с дополнительной синхроинформацией, дополнительный выход накопителя проверок кода 12 через ключ 18 соединен с сумматором по модулю два 19.

В предложенном устройстве уменьшена вероятность ложной синхронизации.

Формула изобретения

Устройство цикловой синхронизации для блоч ных кодов, содержащее на передающей стороне последовательно соединенные кодирующий блок, к управляющему входу которого подключен распределитель, и сумматор по модулю два, а на приемной стороне — последовательно соединенные входной регистр сдвига, выходы которого подключены к блоку вычисления проверок кода, сумматор по модулю два и декодируилций блок, к управляющему входу которого подключен выход генератора тактовых импульсов через делитель частоты, а также дешифратор, от ли чаю ще еся тем, что, с целью уменьшения вероятности ложной синхронизации, в него введены на передающей стороне последовательно соединенные анализатор проверок кода, элемент задержки и ключ, а на приемной стороне — накопитель проверок кода, элемент НЕТ, ключ и дополнительные сумматоры по модулю два, при этом на передающей стороне второй выход распределителя через ключ подключен ко второму входу сумматора по модулю два, выход которого подключен ко входу анализатора проверок кода, а на приемной стороне — выходы блока вычисления проверок кода подключены ко входам соответствующих дополнительных сумматоров по модулю два непосредственно и через накопитель проверок кода, выход которого подключен ко второму входу

557499

Составитель Г. Челей

Техред 3. Фанта

Редактор Г. Петрова

Корректор Д. Мельниченко

Заказ 1110/64

Тираж 815 Подписное

ПНИИПИ Госудваственного комитета Совета Министров СССР по делам изо6ретений и открытий

113035, Москва, Ж- 35, Раушс кая нао., л. 4/S

Филиал ППП" Патсит ", г. ужгород, ул. Пр(скгпая,4 сумма гора l10 модулю два через ключ, к управляю- щему входу которого подключен выход дешифратора, который подключен к управляющему входу элемспта НЕТ, включенного между выходом генератора тактовых импульсов и входом делителя частоты.

Источники информации, принятые 80 внимание при экспертизе:

L. Блейхман В. С Синхронизирующие свойства смежных классов циклических кодов, Вопросы радиоэлектроники, серия Х1, Техника проводной связи, вьш. 7, стр. 47-52, 1966.