Устройство цикловой синхронизации для групповых кодов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву (22) Заявлено 28.04.75 (21) 2128578/09 с присоединением заявки № (23) Приоритет (51) И. К

Н 04 Ь 7/08

Государственный комитет

Совета Министров СССР оо делам изаоретений н открытий (43) Опубликовано 05,05.77,Бюллетень № 17 (53) УДК 621.394.

° 662.2 (088.8) (45) Дата опубликования описания 27,06.77

И, Ф. Хомич (72) Автор изобретении

Пензенский завод-ВТУЗ при заводе ВЭМ (филиал Пензенского политехнического института) (71) Заявитель (54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАБИИ

ДЛЯ ГРУППОВЫХ КОДОВ

Изобретение относится к устройствам передачи данных и может использоваться в системах связи с использованием кодирования информации корректирующими кодами.

Известно устройство цикповой синхрониза- 5 ции для групповых кодов, содержащее на передающей стороне кодирующее устройство корректирующего кода, соединенное с цикловым. распределителем., а на приемной стороне -входной регистр сдвига с узлом вы- ip числения системы проверок кода, генератор тактовых импульсов, соединенный через элемент HET с делителем частоты, и декодируюшее устройство корректирующего кода (11

Недостаток известного устройства состоит в том, что оно имеет высокую вероятность ложной синхронизации при сильной корреляционной зависимости в информационных знаках последовательности передаваемых20 кодовых комбинаций.

Известно также устройство цикловой синхронизации для групповых кодов, содержащее на передающей стороне последовательно соединенные кодер, к управляющему входу кото-25 рого подключен выход циклового распределителя, и сумматор по модулю два, а на приемной стороне — первый и второй регистры сдвига, блок вычисления проверок кода (ВПК), блок сумматоров по модулю два, декодер, к управляющему входу которого подключен выход генератора тактовых импульсов через последовательно соединенные элемент

НЕТ и делитель частоты, а также ключ f2) .

Однако известное устройство имеет невысокую точность выделения сигналов синхронизации, так как при передаче дополнительной информации о (п-к) несинхронных сдвигах путем суммирования с проверочными знаками кода не полностью реализуется возможность правильного определения синхронного положения.

Белью изобретения является повышение точности выделения сигналов синхронизации.

Для этого в устройство цикловой синхронизации для групповых кодов, содержащее на передающей стороне последовательно соединенные кодер, к управляющему входу которого подключен выход циклового рас557502 пределителя, и сумматор по модулю два, а на приемной стороне-первый и второй регистоы сдвига, блок вычисления проверок кода (ВПК),, блок сумматоров по модулю два, декодер,.к управляющему входу которого подключен выход генератора тактовых импульсов через последовательно соединенные элемент НЕТ и делитель частоты, а также ключ, на передающей стороне введен блок вычисления корреляционных зависимос-.ей 10 (ВКЗ), ко входам. которого подключены вход и выход кодера, а выход — ко второму входу сумматора по модулю два„а на приемной стороне введены блок вычисления корреляционных зависимостей (ВКЗ) и элемент И, 15 при этом. выходы разрядов первого и, вто)рого регистров сдвига через блок ВКЗ подключены к одним входам элемента И и ко входам ключа, к управляющим входам которых подключен выход делителя частоты, а 20 выходы блока сумматоров по модулю два, включенного между выходом первого регистра сдвига и входом, второго регистра сдвига, через блок ВПК подключены к другим входам элемента И, выход которого подклю- Ю чен к запрещающему входу элемента НЕТ.

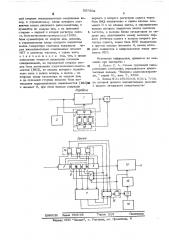

На чертеже изображена блок-схема лредложенного у"тройства.

Устройство цикловой синхронизации для групповых кодов содержит на передающей стороне последовательно соединенные кодер1, к управляющему входу которого подключен выход циклового распределителя 2, блок вычисления корреляционных зависимостей (ВКЗ) 3 и сумматор 4 по модулю два, а

35 на приемной стороне — первый 5 и второй

6 регистры сдвига, блок 7 вычисления проверок кода (BITK), блок 8 сумматоров по модулю два, ключ 9„генератор тактовых имлульсов 10, элемент НЕТ 11, делитель

40 частоты 12, декодер 13, блок вычисления корреляционных зависимостей 14 (ВКЗ) и элемент И 15.

Блок вычисления корреляционных зависи45 мостей 3 может быть выполнен, например, в виде коммутатора 16, соединенного через блок сумматоров 17 по модулю два с накопителем 18.

K управляющему входу декодера 13 под50 ключен выход генератора тактовых импульсов через последовательно соединенные элемент НЕТ 11 и делитель частоты 12. Входы блока 3 ВКЗ подключены ко входу и вых<>ду кодера 1, а выход — ко второму входу сумматора 4 по модулю два. Выходы разрядов первого 5 и второго 6 регистров сдвига через блок 14 ВКЗ подключены к одним входам элемента И и ко входам ключа 9, к управляющим входам которых подключен выход делителя частоты 12. Выходы блока 8 сумматоров по модулю два, включенного между выходом первого регистра сдвига и входом ры истра сдвига „через блок 7 ВПК подключены к другим входам элемента И 15, выход которого подключен к запрещающему входу элемента HET 11.

Предлсженное устройство работает следующим образом.

На передаче информация кодируется групповым (и, к) кодом в кодере 1, управляемым цикловым распределителем 2, и одновременно сс входа и выхода кодера поступает в блок 3 ВКЗ между знаками последовательно передаваемых кодовых комбинаций. Информация о корреляционных соотношениях считывается с накопителя 18 и далее складывается с проверочными знаками кода в сумматоре 4 по модулю два. В результате в канал связи передается дополнительная информация о корреляционных связях между информационными знаками.

На приеме закодированная последовательность накапливается в первом. 5 и втором 6 регистрах сдвига, включенных между выходом и входом блока 8 сумматоров по модулю два. При помощи блока 7 ВПК и блока 14 вычисления корреляционных зависимостей образуются соответствующие результаты проверки, которые для синхронного сдвига кодовой последовательности должны совпадать при отсутствия ошибок, вносимых каналом связи, В результате этого сигнал с элемента И 15 запретит прохождение имлульса на элемент HET 11. В результате делитель частоты 12, связанный с генератором 10 тактовых импульсов, не изменит цикловой фазы. Ключ 9, управляемый от делителя частоты 12, позволяет исключать дополнительную информацию из проверочных знаков кода, которые поступают на декодер 13. При несовпадении результатов сравнения на элементе И 15 элемент.НЕТ

11 запрещает прохождение одного из тактовых импульсов и делитель частоты 12 изменяет фазу, осуществляя анализ кодовой последовательности на других сдвигах до захвата синхронного положения.

Таким образом, в предложенном устройстве повышается точность выделения сигналов синхронизации в системах передачи данных, использующих групповые корректирующие коды.

Формула изобретения

Устройство цикловой синхронизации для групповых кодов, содержащее на передаю557502»

Прием

БНИИПИ Заказ 989/65 Тираж 815 Подписное ф щ ППП «Патент» „ужгород, ул. Проектная, 4 шей стороне последовательно соединеные кодер, к управляющему входу которого подключен выход циклового распределителя, и сумматор по модулю два, а на приемной стороне — первый и второй регистры сдвига, блок вычисления проверок кода (БПК), блок сумматоров по модулю два, декодер, к управляющему входу которого подключен выход генератора тактовых импульсов через последовательно соединенные элемент И

НЕТ и делитель частоты, а также ключ, о т л и ч а ю ш е е с я тем, что, с целью повышения точности выделения сигналов синхронизации, на передающей стороне введен блок вычисления корреляционных зависи- $5 мостей (ВКЗ), ко входам которого подключены вход и выход кодера, а выход — ко второму входу сумматора по модулю два, а на приемной стороне введены блок вычисления корреляционных зависимостей (ВКЗ)Ю и элемент И, при этом выходы разрядов

Пврйпча первого и второго регистров сдвига через блок ВКЗ. подключены к одним входам. элемента И и ко входам. ключа,. к управляющим. входам которых подключен выход делителя частоты, а выходы блока сумматоров по модулю два, включенного между выходом первого регистра сдвига и входом второго регистра сдвига, через блок ВПК подключены к другим входам элемента И, выход которого подключен к запрещающему входу элемента НЕТ, Источники информации, принятые во внимание при экспертие:

1. Квято С. А. Схемы групповой синхронизации сообщений, передаваемых циклическими кодами, "Вопросы радиоэлектроники, " серия Х1, вып. 7, 1966.

2. Заявка No. 21 18596/09, Н 04 L 7/08, по которой принято положительное решение о выдаче авторского свидетельств