Устройство для коррекции цветовых искажений на выходе цветной передающей камеры

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (») 557517 (61) Дополнительное к авт. свид-ву (22) Заявлено 12. 12.74 (21) 2084188/09 с присоединением заявки № (23) Приоритет (43) Опубликовано 05.05,77 Бюллетень № 17 (45) Дата опубликования описания 27.06.77 (51) M. Кл

Н 04 N 9/53

Государственный комитет

Совета Министров СССР

ilo делам изобретений и открытий (53) УДК621.397 (088.8) (72) Автор изобретения

C. B. Никифоров (71) Заявитель

Ленинградский электротехнический институт связи им. проф. М. А. Бонч-Бруевича (54) УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ЦВЕТОВЫХ ИСКАЖЕНИЙ

HA ВЫХОДЕ ЦВЕТНОЙ ПЕРЕДАЮШЕЙ КАМЕРЫ

Изобретение относится к телевиденик, может использоваться в аппаратуре цветного телевизионного вешания и специального назначения для улучшения цветовоспроизведения. б

Известно устройство для коррекции цветовых искажений на выходе цветной передающей камеры, содержащее последовательно включенные буферный усилитель,корректирующий усилитель и сумматор, формиро- 10 ватель цветоразностных сигналов и матрицу, подключенную выходом ко второму входу сумматора, а вход формирователя цветоразностных сигналов подсоединен к выходу буферного усилителя (1) . 15

Однако известное устройство характеризуется точностью коррекции цветовых искажений из-за несовершенства оценки оператором качества цветопередачи.

Цель изобретения — повышение точности 20 коррекции.

Для этого в устройство для коррекции цветовых искажений на выходе цветной передающей камеры, содержащее последовательно включенные буферный усилитель кор- > ректируюший усилитель и сумматор, формирователь цветоразностных счгналов и матрицу, подключенную выходом. ко второму входу сумматора, а вход формирователя цветоразностных сигналов подсоединен к выходу буферного усилителя, введены блок програм.мирования и последовательно включенные вычислитель, блок памяти и блок согласования, выход которого подключен к управляемому входу матрицы, второй вход блока памяти и первый вход вычислителя подключены соответственно к первому и второму выходам, блока программирования, а второй, третий и четвертый входы вычислителя — соответственно к первому, второму и третьему входам буферного усилителя.

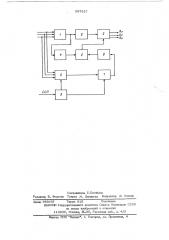

На чертеже изображена структур-.:ая электрическая схема устройства.

Устройство содержит последовательно соединенные буферный усилитель 1, корректирующий усилитель 2 и сумматор 3,. а также последовательно соединенные формирователь цветоразностных сигналов 4 и матрицу 5, подключенную выходом ко второму входу сумматора 3 (вход формирова557517 мирует эти сигналы из сигналов синхронизации приемников).

B данном. устройстве требуемые коэффициенты корректирующей матрицы при передаче оптического испытательного изображения определяются автоматически с помощью вычислителя. При этом, качество цветопередачи объективно оценивается по напряжениям на выходах камеры, и по

)p этим напряжениям. вычисляются оптимальные для данного случая коэффициенты корректирующей матрицы. Таким. образом устраняются погрешчости коррекции, возникающие из-за несовершенства оценки качест15 ва цветопередачи оператором.

Кроме того, оптимальные коэффициенты корректирующей матрицы определяются одновременно с коррекцией цветовых искажений, т.е. учитываются конкретные условия

20 работы передающей камеры, Это позволяет повысить точность коррекции цветовых искажений. теля цветоразностных сигналов 4 подсоединен к выходу буферного усилителя 1), последовательно соединенные вычислитель

6, блок памяти 7 и блок согласования 8, выход которого подключен к управляемому входу матрицы 5 (второй вход блока памяти 7 и первый вход вычислителя 6 подключены соответственно к первому и вто9 р ому выходам блока программирования а второй, третий и четвертый входы вычислителя 6 подсоединены соответственно к первому, второму и третьему входам буферного усилителя 1).

Устройство работает следующим обраУстройство для коррекции цветовых искажений на выходе цветной передающей камеры, содержащее последовательно включенные буферный усилитель корректирующий усилитель и сумматор, формирователь цветоразпостных с. риалов и матрицу, подключенную выходом, ко второму входу сумматора, Q вход формирователя цветоразностных сигналов подсоединен к выходу буферного усилителя, о т л и ч а ю щ е е с я тем., что, с целью повышения точности коррекции, в него введены блок программирования и последовательно включенные вычислитель блок памяти и блок согласования, выход которого подключен к управляемому входу матрицы, второй вход блока памяти и первый вход вычислителя подключены соответственно к первому и второму выходам блока программирования, а второй, тре» тий и четвертый входы вычислителя — соответственно K первому, второму и треть ему входам буферного усилителя.

Источники информации, принятые во внимание при экспертизе:

1. Патент Великобритании М 1268936, кл, Н 4 7, 31. 03. 69. зом.

Выходные сигналы R 5 и 5 передаютг чт шей камеры цветногс -eneaèäåïèÿ () поступают на формирователь цветоразностных сигналов 4. Выходы формирователя соединены со входами матрицы 5, в которои склад складываютсч цветоразностные сигналы.

Корректирующие сигналы с матрицы 5 поступают на сумматор 3„на друго= вход которого подводятся некоррект.: и .ор ектированные 25 Ф о р м. у а и з о б р е т е н и я выходные сигналы R Q-, В передающеи KGMGpbI UT уснленные по мощности и ю задержанные во времении соответствепно буферным 1 и корректирующим 2 усилителями. На вь ходе сумматора ф рмируются скорректированные сигналы 7» содержащие минимизированную о ошибку цветопередачи камеры UÏ.

На вычислитель 6 поступают сигналы

Я Q. В передающей камеры. Вычис35

> Р литель 6 по величине этих сигналов рассчитывает коэффициенты корректирующей матрицы 5 по заданному алгоритму. Ðåз льтаты вычислений запоминаются блое 40 ком памяти 7 и сохраняются в течение всего времени коррекции. Выход блока памяти 7 соединен со входом, блока согласования 8, который преобразует кодированные сигналы с блока памяти в сигналы управляющие работои исполнительнь х э органов корректирующей матрицы 5. Необходимые последовательность и скорость вычислительных операций вычислителя

6 а также запись и перезапись полученэ ной информации в блоке памяти 7 обеспечиваются управляющими сигналами, поступающими на управляемые входы этих блоков с блока программирования 9 (блок 9 фор557517

Ro

&o

Во

Составитель Е.Погиблов

Редактор Б, Федотов Техред N. Левицкая Корректор Ж. Кеслер

Заказ 989/65 Тираж 815 Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4