Устройство для одновременного выполнения операций сложения над множеством чисел

Иллюстрации

Показать всеРеферат

ОП ИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 14.07.75 (21) 2156109/24 с присоединением заявки № (23) Приоритет

Опубликовано 15.05.77. Бюллетень № 18

Дата опубликования описания 06.07.77 (51) М. Кл. G 06F 7/385

Государственный камитет

Совета Министрае СССР аа делам изабретений и аткрытий (53) УДК 681.325.5 (088.8) (72) Авторы изобретения (71) Заявитель

Г. М. Луцкий, Ю..А. Кулаков и А. Н. Долголенко

Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистической революции (54) УСТРОЙСТВО ДЛЯ ОДНОВРЕМЕННОГО ВЫПОЛНЕНИЯ

ОПЕРАЦИЙ СЛОЖЕНИЯ НАД МНОЖЕСТВОМ ЧИСЕЛ

Изобретение относится к области вычислительной техники.

Известны устройства, с помощью которых можно выполнять сложение последовательности чисел (1, 2).

Однако такие устройства не могут одновременно выполнять сложение более чем одной пары операндов, кроме того, они обладают низкой производительностью.

Известны также многорегистровые устройства, основанные на конвейерном методе обработки информации (3).

Эти устройства допускают одновременное выполнение операций сложения над множеством пар операндов, однако не выполняют многоместные операции сложения, т. е. операции, в которых участвуют более двух операндов. Это ограничивает производительность данных устройств для отдельно взятых программ, если они не допускают полного распараллеливания. Например, при выполнении последовательности команд, где каждая р-я команда использует результаты, полученные с помощью (р — 1) -й команды, данная р-я команда выполняется только после завершения операции, выполняемой на основе (р— — 1)-й команды, т. е. после прохождения информации через все блоки конвейерного устройства.

Известны устройства для одновременного выполнения арифметических операций над множеством чисел, состоящие из однотипных блоков, причем каждый -й блок содержит регистр частичного результата, узел формирования частичного результата, триггер хранения младшего разряда частичного,результата, триггер формирования окончательного результата, элемент И, выходы и старших разрядов узла формирования частичного ре10 зультата соединены с входами регистра частичного результата (i+I ) -го блока, единичный выход триггера хранения младшего разряда частичного результата соединен с первым входом элемента И, второй вход которо15 го соединен с единичным входом триггера формирования окончательного результата (i+1)-го блока и единичным выходом триггера формирования окончательного результата данного блока, единичный вход которого свя20 зан с единичным выходом триггера формирования окончательного результата (i+1) -го блока, выход младшего разряда узла формирования частичного результата подключен к единичному входу триггера хранения млад25 шего разряда частичного результата, нулевые входы триггеров хранения младшего разряда частичного результата, формирования окончательного результата и регистра частичного результата подключены к шине такто30 вых импульсов.

558276

p — a . 2(b + b 2л + c. 2 р-1

С помощью этого устройства можно вычислить выражение р = а„х" + ал х"- +... + а,х -{- а„ следовательно, можно вычислять выражение р=a„2" +ал (2" — +... +а,.2+а„ т. е. производить операцию сложения с плавающей запятой, Но выполнение операции сложения в этом случае затруднено. Так, например, нахождение .суммы где n=p — s, m=p — r сводятся к вычислению выражения

p = (... (((а.2+0)+0)2+ .+0) 2(-Ь) 2+... +

+ О) 2 + с) 2 +... + 0) 2, что требует использования большого числа уровней, и, следовательно, значительного времени вычисления.

Целью предполагаемого изобретения является повышение быстродействия сложения последовательности чисел с плавающей запятой.

Поставленная цель достигается тем, что в

i-й блок устройства введены регистр порядка, узел формирования порядка, элемент ИЛИ и два логических узла, причем выходы регистра порядка соединены со входами узла формирования порядка, выходы которого подключены ко входам регистра порядка (i+1)-го блока, кроме того выходы регистра порядка соединены со входами элемента ИЛИ, выход которого соединен с суммирующим входом узла формирования порядка, а также с управляющими входами логических узлов, выходы регистра частичного результата соединены с входами логических узлов, выходы первого логического узла подключены к входам п старших разрядов узла формирования частичного результата, а выходы второго логического узла подключены к входам (п+1) разряда узла формирования частичного результата, причем п-й выход второго логического узла подключен к п-му и (п+1)-му входам узла формирования частичного результата, к суммирующему входу которого подключен единичный выход триггера хранения младшего, разряда частичного результата, выход элемента И соединен .с (п — 1) -ным разрядом регистра частичного результата (i+1) -ro блока.

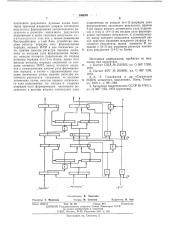

На чертеже изображена функциональная схема i-го (i+1)-го блоков устройства.

Каждый 1-ый блок устройства состоит из регистра 1 порядка, регистра 2 I-го частичного результата, триггера 3 хранения младшего .разряда (1+1) -го частичного результата, триггера 4 формирования окончательного ре5

25 зо

6О

65 зультата, узла 5 формирования порядка, элемента ИЛИ 6, управляющего формирования порядка и (l+1)-ой частичной суммы, узла

7 формирования (1+1)-го частичного результата, элемента И 8, первого логического узла

9 и второго логического узла 10.

Указанные узлы связаны между собой следующими простыми связями: выход триггера знака порядка и инверсные выходы триггеров значения порядка регистра 1 порядка соединены с входами узла 5 формирования порядка, выходы регистра 1 порядка — с входами элемента ИЛИ 6, причем вход знака порядка соединен с инверсным входом элемента ИЛИ 6, а выходы значения порядка имеют связи с входами элемента ИЛИ 6 только тех разрядов, которые соответствуют наличию единиц в обратном коде « — r», где

2 — "(А (.2", А — область представления чисел в машине, выход элемента ИЛИ 6 соединен с управляющим входом логических узлов 9, 10 и с суммирующими входом узла 5 формирования порядка, выход знакового разряда и инверсные выходы разрядов порядка узла 5 формирования порядка, выход знакового разряда и инверсные выходы разрядов порядка узла 5 формирования порядка связаны с входами регистра порядка, причем узел 5 формирования порядка устранен таким образом, что перенос в знаковый разряд сопровождается переносом в младший разряд порядка, п старших разрядов узла 7 формирования частичного результата соединены с входами (регистра 2 частичного результата (i+1)-ro блока, п выходов регистра 2 частичного результата соединены,с п входами логических узлов 9 и

10, п выходы логического узла 9 соединены с входами п старших разрядов узла 7 формирования частичного результата, п выходы логического узла 10 — с (п+1) -входами узла формирования частичного результата, причем и-ый выход логического узла 10 соединен с и-ым и (п+1)-ым входами узла формирования частичного результата 7, выход триггера

3 хранения младшего разряда частичного результата соединен со входом элемента И 8 и с суммирующим входом узла формирования частичного результата, выход элемента И 8 соединен с (n — 1)-ым входом регистра 2 частичного результата (i+1) -го блока, выход триггера 4 формирования окончательного результата соединен с входом элемента И 8 и входом триггера формирования окончательного результата (i+1)-го блока, вход триггера формирования окончательного результата соединен с выходом триггера формирования окончательного результата (i — 1) -го блока, выход младшего разряда узла формирования частичного результата соединен с входом триггера хранения младшего разряда частичного результата, нулевые входы всех триггеров и регистров подключены к шине тактовых импульсов.

558276

15 тактов.

На

Зо

Работа устройства происходит следующим образом.

Мантисса и ее знак первого слагаемого последовательности принимаются в дополнительном коде на регистр 2 частичного результата, а его порядок со своим знаком принимается на регистр 1 порядка первого блока.

В следующем такте содержимое регистра 1 порядка передается через узел 5 формирования порядка в регистр 1 порядка следующего блока, а содержимое регистра 2 частичного результата через первый логический узел 9 или второй логический узел 10, а через узел

7 формирования частичного результата передается в регистр 2 частичного результата следующего блока, п ри этом на регистры 1 и 2 принимаются соответственно порядок и мантисса следующего числа, причем в зависимости от сигнала на выходе элемента ИЛИ б либо порядок в процессе передачи в следующий блок уменьшается на единицу, а мантисса при этом остается без изменений (содержимое триггера 3 хранения младшего разряда частичного результата не меняется), либо порядок передается в следующий блок без изменения, а мантисса складывается с содержимым триггера 3 хранения младшего,разряда частичного результата, старшие из разрядов полученного таким образом частичного результата передаются в регистр 2 частичного результата последующего блока, а младший разряд этого частичного результата записывается в триггер 3 хранения младшего разряда частичного результата. Этому варианту соответствует код 0 на выходе элемента

ИЛИ б, который возможен только в том случае, если в регистре 2 порядка записывается код порядка « — г», передачи числа из регистра частичного результата на узел 7 формирования частичного результата происходит через логический узел 10 через логический узел 9. Логический узел 10 соединен с узлом формирования частичного результата, что позволяет производить сложение в дополнительном модифицированном коде. Последующий прием и старших разрядов частичного результата регистра частичного результата следующего блока и младшего разряда триггером хранения младшего разряда частичного результата является нормализацией частичного результата. Описанные преобразования повторяются для каждого из rn блоков для 1 операндов.

Если необходимо сложить 1 чисел, то необходимо использовать г2r+1

1+ entier — а + 1 и уровней, где и — разрядность мантиссы; а— б. м.

Для формирования результата в течение (1+ 1) —: l+ entier m + 1 тактов в триггер формирования окончательного результата записывается код «1», а в регистр 1 порядка « — » в обратном коде. В этом случае состояние триггера 3 хранения младшего разряда частичного результата передается через элемент И 8 в (n — 1)-ый разряд регистра 2 частичного результата следующего блока. Код данного регистра сдвигается на каждом такте на один разряд вправо, а к моменту окончания сложения оказывается на нужном месте.

Полная сумма последовательности из l чисел может быть получена за

1+ 2 (1 + r) + entier — u и

l+entier + 2 = ом такте можно принимать новую последовательность чисел для сложения, следовательно, основное преимущество конвейерного метода обработки информации, которая заключается в эффективном использовании аппаратуры многорсгистровых устройств, в данном случае сохраняется.

Выполнение операций сложения над числами с плавающей запятой при помощи данного устройства происходит быстрее, требует более простого устройства управления и исключает необходимость в специальной организации памяти.

С помощью предложенного устройства, наряду с сложением последовательности чисел с плавающей запятой, возможно выполнение сложения чисел с фиксированной запятой, сдвига чисел.

Формула изобретения

Устройство для одновременного выполнения операций сложения над множеством чисел, состоящее из однотипных блоков, причем каждый 1-ый блок содержит .регистр частичного результата, узел формирования частичного результата, триггер хранения младшего разряда частичного результата, триггер формирования окончательного результата, элемент И, выходы и старших разрядов узла формирования частичного результата соединены со входами регистра частичного результата (i+1)-го блока, единичный выход триггера хранения младшего разряда частичного результата соединен с первым входом элемента И, второй вход которого соединен с единичным входом триггера формирования окончательного результата (i+1)-го блока и единичным выходом триггера формирования окончательного результата данного блока, единичный вход которого связан с единичным выходом триггера формирования окончательного результата (i — 1) -ro блока, выход младшего разряда узла формирования частичного результата подключен к единичному входу триггера хранения младшего разряда

-598276, уоря&л."

Составитель В. Березкин

Техред М. Семенов .

Корректор Н. Аук

Редактор T. Морозова

Заказ 1258/11 Изд. Ма 451 Тираж 815 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, K-35, Раушокая наб., д. 4/5

Типография, пр. Сапунова, 2 частичного результата, нулевые входы триггеров хранения младшего разряда частичного результата, формирования окончательного результата и регистра частичного результата подключены к шине тактовых импульсов, о тл и ч а ю щ ее с я тем, что, с целью повышения быстродействия, в i-ый блок устройства введены регистр порядка, узел формирования порядка, элемент ИЛИ и два логических узла, причем выходы регистра порядка соединены со входами узла формирования порядка, выходы которого подключены ко входам регистра порядка (i+1)-го блока, кроме того выходы регистра порядка соединены со входами элемента ИЛИ, выход которого соединен с суммирующим входом узла формирования порядка, а также с управляющими входами логических узлов, выходы регистра частичного,результата соединены со входами логических узлов, выходы первого логического узла подключены ко входам и старших разрядов узла формирования частичного результата, а выходы второго логического узла подключены ко входам (и+1) -разрядов узла формирования частичного результата, причем и-ый выход второго логического узла подключен к и-му и (п+1)-му входам узла формирования частичного результата, к суммирующему входу которого, подключен единичный выход триггера хранения младшего разряда частичного результата, выход элемента И соединен с (n-1)-ым разрядом регистра частич10 ного результата (i+1) -го блока.

Источники информации, прийятые во внимание при экспертизе:

15 1. Патент США № 3535502, кл. G 06F 7/385, 1970.

2. Патент ФРГ № 2034841, кл. G 06F 7/38, 1973.

3. К. Г. Самофалов и др. «Структуры

20 ЭЦВИ четвертого поколения», Киев, Техника, 1972 г., с. 89 — 248.

4. Авторское свидетельство СССР № 479111, кл. G 06F 7/52, 1973 (прототип).