Устройство для многоуровневой кодоимпульсной модуляции

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (1Ц 559416

lt !

0 с

:Ъ (61) Дополнительное к авт. свид-ву (22) Заявлено 04.05.75 (21) 2133l46/09 с присоединением заявки № (23) Приоритет (43) Опубликовано25.05.77.Бюллетень № l (45) Дата опубликования описания 18.07.77 (51) М. Кл.о

Н 04 L 3/00

Н 03 К 7/00

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий (53) УДК 621, 396. .436.4(088.8) (72) Автор изобретения

В. Н. Бакеев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ МНОГОУРОВНЕВОЙ

КОДОИМПУЛЬСНОЙ МОДУЛЯЦИИ

Изобретение относится к электросвязи и может нспопьзоваться при передаче информации по каналам связи с помощью многоуровневой кодоимпупьсной модуляции (КИМ).

Известно устройство дпя многоуровневой кодоимпупьсной модуляции, содержащее последовательно соединенные преобразователь кода и блок изменения полярности импульс- 10 ного сигнала, соединенный с выходной шиной и с интегрирующей схемой определения полярности сигнала (11.

Однако в известном устройстве интегри- 15 рующая схема определения полярности сигнала выполнена в виде аналогового интегратора, точность, которого зависит от изменения амплитуды и полярности сигнапа, т. е. от значения передаваемого кода. 20

Снижение точности работы интегрирующей схемы опредепения попярности сигнапа приводит к увеличению низкочастотной составпяющей в выходном сигнапе устройства. 25

Цепь изобретения — уменьшение низкочастотной составпяющей выходного сигнапа.

Дпя этого в устройство дпя многоуровневой кодоимпупьсной модуляции введены накапливающий сумматор, логический сумматор, элемент ИЛИ, инвертор, элемент задержки, триггер, четыре элемента И, две схемы совпадения и формирователь допопнитепьного кода, выход которого через последовательно соединенные первую схему совпадения, логический сумматор, накапливающий сумматор и элемент ИЛИ подключен к первым входам первого и второго элементов И, выходы которых через триггер подключены к дополнительным входам блока изменения полярности импульсного сигнала и к первым входам третьего и четвертого элементов И, выходы которых соединены соответственно со вторыми входами первой и второй схемы совпадения. При этом первый вход второй схемы совпадения соединен с входами преобразователя кода и формирователя дополнительного кода, а выход через второй

559416

55 вход логического сумматора-с накапливающим сумматором, второй выход которого подключен ко второму входу первого элемента И непосредственно, а ко второму входу второго элемента И вЂ” через инвертор. Причем выход элемента задержки соединен со вторыми входами третьего и четвертого элементов И, а на тактовые входы первого и второго элементов И и на вход элемента задержки поданы импульсы 10 синхронизации.

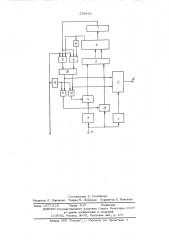

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство содержит последовательно соединенные преобразователь кода 1 и блок

2 изменения полярности импульсного сигнала, а также формирователь дополнительного кода 3, выход которого через последовательно соединенные первую схему сов- 20 падения 4, логический сумматор 5, накапливающий сумматор 6 и элемент ИЛИ 7 подключен к первым входам первого 8 и второго 9 элементов И. Выходы последних через триггер 10 подключены к допол- 25 нительным входам блока 2 изменения полярности импульсного сигнала и к первым входам третьего 11 и четвертого 12 элементов И, выходы которых соединены соответственно с вторыми входами первой 4 и 30 второй 13 схем совпадения, При этом первый вход второй схемы совпадения 13 соединен со входами преобразователя кода 1 и фор .ирователя дополнительного кода 3, а выход — через второй вход логического 35 сумматора 5 — с накапливающим сумматором

6, второй выход которого подключен ко второму входу первого элемента И 8 непосредственно, а ко второму входу второго элемента И 9 через инвертор 14. 40

Устройство также содержит элемент задержки 15, выход которого соединен со вторыми входами третьего 11 и четвертого 12 элементов И, а на тактовые входы первого 8 и второго 9 элементов И и на вход элемен- 45 та задержки 1 5 поданы импульсы синхронизации.

Устройство работает следующим образом.

Передаваемый код, поступающий от источника информации, преобразуется в преоб- 50 разователе кода 1 в импульсный сигнал с амплитудой, соответствующей передаваемому коду, который подается на вход блока

2 изменения полярности импульсного сигнала. Одновременно с поступлением каждого значения передаваемого кода от источника информации поступает импульс синхронизации, который подается на входы элементов И 8 и 9, а также на вход элемента задержки 15.

В случае, когда накапливающий сумматор 6 содержит положительный код, т. е. знаковый разряд находится в нулевом состоянии, импульс синхронизации, проходя через элемент И 9, устанавливает триггер

10 в нулевое состояние.

Сигнал с нулевого выхода триггера 10 поступает на блок 2 изменения полярности импульсного сигнала, который устанавливает отрицательную полярность импульсного сигнала на выходной шине 16. Одновременно сигнал с нулевого выхода триггера 1 0 разрешает прохождение задержанного на элементе задержки 15 импульса синхронизации через элемент И 12 на входы схемы совпадения 4. При этом дополнительный код с выхода формирователя дополнительного кода 3 поступает через схему совпадения 4 и логический сумматор 5 на входы накапливающего сумматора 6.

В результате этого от содержимого накапливающего сумматора 6 вычитается текущее значение передаваемого кода. B случае, когда накапливающий сумматор

6 содержит отрицательный код, т. е. знаковый разряд находится в единичном состоянии, импульс синхронизации проходит через элемент И 8 и устанавливает триггер 10 в единичное состояние.

Сигнал с единичного выхода триггера

10 поступает на блок 2 изменения полярности, который устанавливает положительную полярность импульсного сигнала на выходной шине 16. Одновременно сигнал с единичного выхода триггера 10 разрешает прохождение задержанного импульса синхронизации с выхода элемента задержки

1 5 через элемент И 1 1 на входы схемы совпадения 13. При этом передаваемьгй код с входных кодовых шин 17 поступает через схему совпадения 13 и логический сумматор 5 на входы накапливающего сумматора 6. В результате этого с содержимым накапливающего сумматора 6 складывается текущее значение передаваемого кода.

Таким образом, изменение полярности импульсного сигнала с амплитудой, соответствующей текущему значению передаваемого кода, производится в зависимости от содержимого накапливающего сумматора 6, т. е. от результата сложения и вычитания всех предшествующих значений передаваемого кода.

В случае, когда содержимое накапливающего сумматора 6 равно нулю, т. е. ког да числовые разряды находятся в нулевом состоянии, с выхода элемента ИЛИ 7 нулевой сигнал запрещает прохождение им559416 пульса синхронизации через элементы И 8 или 9 на входы триггера 10 и последний сохраняет свое прежнее :состояние и при текущем значении передаваемого кода.

Предложенное устройство позволяет практически свести к нулю постоянную составляющую и значительно уменьшить низкочастотную составляющую выходного импульсного сигнала, что позволяет увеличить скорость и достоверность передачи информации по каналам связи.

Формула изобретения

Устройство для многоуровневой кодоимпульсной модуляции, содержащее последовательно соединенные преобразователь кода и блок изменения полярности импульсного сигнала, о т л и ч а ю щ е е с я тем, что, с целью уменьшения низкочастотной составляющей выходного сигнала, введены накапливающий сумматор, логический сумматор, элемент ИЛИ, инвертор, элемент задержки, триггер, четыре элемента

И, две схемы совпадения и формирователь дополнительного кода, выход которого через последовательно соединенные первую схему совпадения, логический сумматор, накапливающий сумматор и элемент ИЛИ подключен к первым входам первого и второго элементов И, выходы которых через триггер подключены к дополнительным входам блока изменения полярности им— пульсного сигнала и к первым входам третьего и четвертого элементов И, выходы которых соединены соответственно со

10 вторыми входами первой и второй схем совпадения, при этом первый вход второй схемы совпадения соединенсвходами преобразователя кода и формирователя дополнительного кода, а выход через второй вход ло1S гического сумматора-с накапливающим сумматором, второй выход которого подключен к второму входу первого элемента И непосредственно, а к второму входу второго элемента И-через инвертор, причем

20 выход элемента задержки соединен со вторыми входами третьего и четвертого элементов И, а на тактовые входы первого и второго элементов И и вход элемента задержки поданы импульсы синхронизации.

25 Источники информации, принятые во внимание при экспертизе:

1. Патент CILIA N 3560856, кл, 325-38, 1967 г. (прототип).

559416

Составитель Е. Погиблова

Редактор Л. Народная Техред М. Левицкая Корректор Л. Власенко

Заказ 1377/110 Тираж 815 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4