Устройство декодирования линейных сверточных кодов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (1Ц @59419 (61) Дополнительное к авт. свид-ву (22) Заявлено03.02.76 (21) 2326773/09 (51) М. Кл.е

Н 04 L 3/02

6 06 F 11/08 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.05.775юллетень №19 (45) Дата опубликования описания18.07.77

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий (53) УДК 621.394.14 (088.8) (72) Автор.: изобретения

B. B. Измалков (71) Заявитель (54) УСТРОЙСТВО ДЕКОДИРОВАНИЯ

ЛИНЕЙНЫХ СВЕРТОЧНЫХ КОДОВ

Изобретение относится к радиоэлектронике и может быть использовано в устройствах декодирования информации, представленной в виде линейных сверточных кодов.

Известно устройство декодирования линейных сверточных кодов, содержащее на входе информационный регистр сдвига, выходы разрядов которого подключены к соответствующим вход м вычислителя синдрома, а также пороговый блок, блоки ум- ð ножения на весовые коэффициенты, информационный регистр, регистр изменений.

Известное устройство имеет низкую на I дежность из-за большого количества оборудования, 15

Ueab изобретения — упрощение устройства.

Для этого в предлагаемое устройство декодирования линейных сверточных кодов, содержащее на входе информационный ре- 20 гистр сдвига, выходы разрядов которого ,подключены к соответствующим входам вычислителя синдрома, а также пороговый блок, введены регистр неравнозначности и первый и второй сумматоры по модулю 25 два. Выход вычислителя синдрома через последовательно соединенные первый сумматор по модулю два, на второй вход которого подана поверочная комбинация сверточного кода, и регистр неравнозначности подключен к входам порогового блока, выход которого и выход информационного регистра сдвига подключены к соответствующим входам второго сумматора по модулю два.

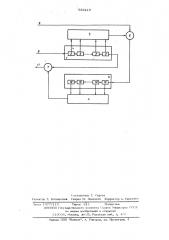

На чертеже изображена структурная электрическая схема предлагаемого уст ройс тва.

Устройство декодирования линейных сверточных кодов содержит информационный регистр сдвига 1, выходы разрядов 2 которого подключены к .. соответствующим входам вычислителя синдрома 3, а также пороговый блок 4, регистр неравнозначност ти 5 и первый 6 и второй 7 сумматоры по модулю два. Выход вычислителя синдро ма 3 через последовательно соединенные первый сумматор 6 по модулю два, на второй вход которого подана поверочная комбинация свер очного кода, и регистр

559419 неравнозначности 5 подключен ко вхо дам порогового блока 4, выход которого и выход информационного регистра сдвига

1 подключены к соответствующим входам второго сумматора 7, по модулю два.

Устройство работает следующим образом.

По шин 8 поступает информационная часть сверточного кода, а цо шине о одновременно с информационной — поверо ная часть сверточного кода (синдром).

С каждым сдвигом информации в информационном регистре сдвига 1 на выходе вычислителя синдрома 3 появляется очередной синдром, получаемый делением кода, хранящегося а информационном регистре сдвига 1, иа образующий многочпен.

Вычисленный синдром поступает на вход первого сумматора 6 по модулю два, где он сравнивается с принятым по шине

9 синдромом,. Если в информационной и оверочной частях кода не было ошибок (сбоев), то вычисленный и принятый синдромы будут совпадать и на выходе первого сумматора по модулю два появится логический "О". В случае неравенства синдромов на выходе сумматора 6 будет логическая "1". Этот сигнал является сигналом неравнозначности и запоминается в регистре неравнозначности 5. Сигналы неравнозначностей, записанные в ячейках памяти 10 регистра неравнозначности 5, поступают в соответствии с образутощпм мпогочневом на входы порогового блока 4, порог срабатывания которого устанавливается в зависимости от минимального кодового расстояния данного сверточного кода. Превышение этого порога говорит о том,что либо произошла ошибка в соответствующем информационном разряде, либо число ошибок превысило допустимое.

Сигнал с порогового блока 4 поступает на один вход второго сумматора 7 по модулю два и изменяет значение информационного разряда, выталкиваемого из информационного регистра сдвига 1 и поступающего на другой вход второго сумматора по .. модулю два.

Таким образом, на выходной шине 11 оказывается последовательный код декодированной информации.

Предлагаемое устройство декодирования линейных сверточных кодов позволяет значительно сократить емкость информацион1Б ного регистра, исключить синдромный регистр, блоки формирования проверок, блоки умножения на весовые коэффициенты, регистр изменений, а также сократить число пороговых элементов до одного.

Формула изобретения

Устройство декодирования линейных сверточных кодов, содержащее на входе информационный регистр сдвига, выходы разрядов которого подключены к соответствующим входам вычислителя синдрома, а также пороговый блок, î т и и ч а ю ш е30 е с я тем, что, с целью упрощения устройства в него введены регистр нер внозначности и первый и второй сумматоры по модулю два, выход вычислителя синдрома через последовательно соединенные первый сумЗ5 матор по модулю два, на второй вход которого подаиа поверочная комбинация свер- точного кода, и регистр неравнозначности подключен к входам порогового блока, выход которого и выход информационного ре40 гистра сдвига подключены к соответствующим входам второго сумматора по модулю два.

558419

Составитель Г. Серова

Редактор Г. Котельский Техред М. Левицкая Корректор Л. )власенко

:)аказ 1 377/110 Тираж 81 5 Поаписнс е

)!))ИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

1 1 3035, Москва, Ж-35, Раушская наб., д 4/5

илиад ППП "Патент", г. Ужгород, ул. Проектная, 4