Анализатор наличия передачи дискретной информации по каналу связи

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

О Л Й С М К И 1 .-

ИЗОБРЕТЕН йЯ

К АВТОР(:МОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено04.01.76 (21) 2309216у09 с присоединением заявки ¹ (23) Приоритет (43) Опубликовано25,06,77.Бюллетень ¹19 (46) Дата опубликования описания 12.07.77 (о1) M. Кл.

Н 04 14 11/08

Государственный комитет

Совета Министров СССР оа делам изобретений и открытий (>>) УДК 621 ° 3О4. ,317 (088,8) В. С, Миронов и Г. С. Миронова (72) Авторы изобретения (71) Заявитель (54) АНАЛИЗА ГОР НАЛИЧИЯ Пт- р дАНИ

ДИСКРЕТНОЙ ИНФЭРМА1тИИ ПО КАНАЛУ СВЯЗИ

Изобретение относится к передаче информации и может использоваться при автоматическом обмене сообщениями в сетях связи.

Известен анализатор наличия передачи дискретной информации по каналу связи, содержащий триггер и два элемента И, выходы которых подключены к входам реверсивного счетчика )lj.

При использовании этого анализатора необходим дополнительный анализ сигнала за-;0 нятости сети, что влечет за собой увеличение времени анализа и потребность в дополнительном оборудовании и повторных запусках анализатора.

С целью уменьшения времени анализа в 15 анализатор наличия передачи дискретной информации по каналу связи согласно изобретению введены два дешифратора, блок формирования и задержки сигнала, элемент ИЛИ и последовательно соединенные блок автома- 20 тической подстройки тактовых частот, дополнительный элемент И и инвертор. Выход инвертора подключен к первому входу первого элемента И, второй вход которого соединен с выходом элемента ИЛИ, к входу которого 25 подключен выход блока формирования и задержки сигнала, выход дополнительного элемента h подключен к первому входу второго элемента И, второй вход которого соединен с входами блока автоматической подстройки тактовых частот, блока формирования и задержки сигнала и вторым входом элемента

ИЛИ, а выходы реверсивного счетчика через соответствующие деп:ифраторы подключены к третьим входам элементов И и к входам триггера.

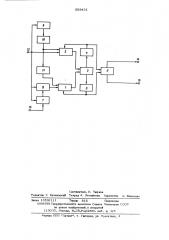

На чертеже представлена структурная электрическая схема предлагаемого анализатора наличия передачи дискретной информации по каналу связи.

Анализатор содержит два элемента И 1, 2, соединенных " входами реверсивного счет. чика 3, два дешифратора 4,5, входы которых соединень: с соответствуюшими выходами реверсивна о счетчика 3, а выходы с соответствующими входами триггера 6, блок 7 формирования и задержки сит.нала,,элемент ИЛИ 9 и последовательно соединенные блок 9 автоматической подстройки тактовых частот, дополнительный элемент

55943 1

И 10 и инвертор 11. Выход инвертора 11 подключен к первому входу первого элемента И 1, второй вход которого соединен с выходом элемента ИЛИ 8, к первому входу которого подключен выход блока 7 форми. рования и задержки сигнала. Выход дополнительного элемента И 10 подключен к первому входу второго элемента И 2, второй вход которого соединен с входами блока 9 автоматической подстройки тактовых ча- 10 стот, блока 7 формирования и задержки сигнала и вторым входом элемента ИЛИ8, Выходы дешифраторов 4,5 соединены соответственно с третьими входами элементов И 21.

Анализатор работает следующим образом.

С подачей тактовых сигналов анализатор автоматически включается в работу.

Поступающие по входу 12 сигналы, соответствующие фронтам применяемых посы- 20 лок, подаются в блок 9 автоматической подстройки тактовых частот, на второй вход элемента И 2, на вход сброса блока

7 формирования и задержки ситнала и через элемент ИЛИ 8 на второй вход элемента И 1. Сигнал с выхода блока 9 asтоматической подстройки тактовых частот поступает на вход дополнительного weмента И 10, с его выхода - на первый вход элемент И 2 и через инвертор 11 на первый вход элемента И 1.

По входу 13 тактовые сигналы посту пают в блок 7 формирования и задержки сигнала, с выхода которого сигнал, вырабатываемый в случае отсутствия сигналов, Зо соответствующих фронтам принимаемых пс сылок, в течение заданного промежутка времени, поступает через элемент ИЛИ 8 на элемент И 1.

С выходов элементов И 1, 2 сигналы 40 проходят на соответствующие входы реверсивного счетчика 3, с его выходов - на входы дешифратора 4 наличия передачи дискретной информации по каналу связи и дешифратора 5 отсутствия передачи дискретной информации по каналу связи. С выходов дешифраторов 4, 5 сигналы поступают соответственно на входы запрета

4 (третьи входы) элементов И 2,1 и на юхоки @ 1 а "0 трnrrepа 6 ф ции состояния. Из триггера 6 сигнал нали чия передачи информации поступает на выход 14 анализатора, а сигнал отсутстЪия передачи информации - на выход 15.

Технико-экономическая эффективнос гь изобретения состоит в уменьшении времени анализа при повышении надежности выделения сигнала наличия передачи информации по каналу связи, а уменьшение времени анализа позволяет повысить пропускную способность сети связи.

Формула изобретения

Анализатор наличия передачи дискретной информации по каналу связи, содержащий триггер и два элемента И, выходы которых подключены к входам реверсивного счетчика, отличающийся тем, что, с целью уменьшения времени анализа, в него введены два дешифратора, блок формирования и задержки сигнала, элемент ИЛИ и последовательно соединенные блок автоматической подстройки тактовых частот, дополнительный элемент И и инвертор, выход которого подключен к первому входу первого элемента И, второй вход которого соединен с выходом элемента ИЛИ, к входу которого подключен выход блока формирования и задержки сигнала, выход дополнительного элемента

И подключен к первому входу второго элемента И, второй вход которого соединен с входами блока автоматической подстройки тактовых частот, блока формирования и задержки сигнала и вторым входом элемента

ИЛИ, а выходы реверсивного счетчика через соответствующие дешифраторы подключены к третьим входам элементов И и к входам триггера.

Источники информации, принятые во внимание при экспертизе:

1, Авторское свидетельство СССР

Nð 319094, М. Кл. Н 04 В 3/04, приор итет 2 9. 04. 7 О.

55943 1

Составитель И. Тюрина

Редактор Г. Котельский Техред А. Лемьанова Корректор А. Власенко

Закаэ 1359/111 ТВрае 815 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам иэобретений и открытий

113О35, Москва, Ж-35,Раушскаи наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4