Цифровой прибор для частотных датчиков

Иллюстрации

Показать всеРеферат

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

560!86

Союз Советских

Социал исти меских

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 07.07.75 (21) 2155547/21 с присоединением заявки ¹ (23) Приоритет

Опубликовано 30.05.77. Бюллетень № 20

Дата опубликования описания 11.07.77 (51) М Кл G OIR 23/00

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.317.761 (088.8) (72) Авторы изобретения

Т. М. Алиев, Э. А, Тургиев, Я. Л. Штейтман и Т. M. Вердиев

Азербайджанский институт нефти и химии им. М. Азизбекова (71) Заявитель (54) ЦИФРОВОЙ ПРИБОР ДЛЯ ЧАСТОТНЫХ ДАТЧИКОВ

Изобретение относится к измерительной технике и может использоваться в информационно-измерительных системах.

Известны приборы для частотных датчиков, состоящие из .входного формирующего устройства, устройства управления, кварцевого генератора, делителя частоты, преобразователя интервала времени в постоянное напряжение, блока линеаризации, блока температурной (аддитивной) поправки, выходного суммирующего усилителя, логических схем и индикатора.

Однако такие приборы имеют недостаточно высокую точность и сложны в эксплуатации.

Цель изобретения — повышение точности прибора.

Это достигается тем, что в цифровой прибор для частотных датчиков, содержащий последовательно соединенные формирователь, блок управления, первый ключ, элемент задержки, последовательно соединенные канал температурной поправки, второй ключ, последовательно соединенные элемент ИЛИ, счетчик, индикатор, а также синтезатор частот, включенный между вторыми входами первого и второго ключей (прпчем второй выход блока управления соединен с входом канала температурной поправки), дополнительно введены последовательно соединенные блок нечетных чисел, дешифратор и сумматор, вторые входы которого соединены с первыми выходами блока формирования нечетных чисел, с выходом олока задержки и Входамп счетчика, а выход — с первым входом элемента ИЛИ, второй вход которого связан с вторым выходом блока формирования нечетных чисел, входы которого соединены с выходами ключей.

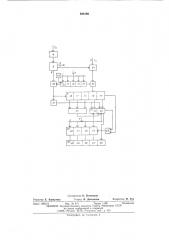

На чертеже приведена блок-схема предла10 гаемого цифрового прибора с пятиразрядным представлением результата измерения и одним каналом аддптпвной (например, температурной поправки.

Блок-схема состоит из шин 1 и 2 установ15 ки коэффициентов а и Ь, входа 3 канала аддитивной поправки, входного формирующего устройства 4, устройства управления 5 с управляющими шинами импульса измерения 6, импульса пуска канала аддитпвной поправки

20 7 и импульса сброса 8, блока формирования

9 Hp÷åòíû÷ чисел, состоящего из пяти декад

10 — 14, делителя частоты 15, состоящего из пяти декад 16 — 20, накапливающего сумматора 21, состоящего нз двух десятичных сумма25 торов 22, 23, канала аддитивной (температурной) поправки 24, счетчика результата 25, состоящего цз четырех декад 26 — 29, ключа 30, схемы задержки импульсов 31, дешпфратора поправки 32, клапана ИЛИ 33, ключа 34, ус30 тройства цифровой индикации 35, состоящегс

560186

1 где а=

УК То

60

65 из пяти индикаторных ламп с дешифраторами 36 — 40, кварцевого генератора 41.

С учетом устанавливаемых коэффициентов а и b формула преобразования, осуществляемого прибором, имеет вид и х= (аТ„) — b+ g С,У,, ю=т

b=—

T„ — текущее значение периода колебаний на выходе датчика;

К вЂ” коэффициент чувствительности; х — значение измеряемого параметра;

С,, U, — коэффициент передачи и сигнал на входе канала аддитивной поправки.

Коэффициенты формулы преобразования а и b устанавливаются на наборных полях в виде двоично-десятичного кода и вводятся через шины 1 и 2 перед началом измерения, причем коэффициент b вводится в дополнительном коде b.

Измеряемый синусоидальный сигнал с периодом Т, подается на входное формирующее устройство 4, где преобразуется в импульсы с периодом следования Т,-, которые затем поступают в устройство управления 5. Выходными сигналами устройства управления являются импульс измерения с длительностью

Т„=1000 Т, (шина 6), импульс пуска канала температурной поправки (шины 7), а также импульс сброса на шине 8, устанавливающий узлы схемы в исходное состояние.

Импульс сброса устанавливает в нулевое состояние блок формирования 9 нечетных чисел (декады 10 — 14), декады 16 — 20 делителя частоты 15, а также подготавливает к работе канал температурной поправки 24. Кроме того, этот импульс через шину 2 устанавливает дополнительный код коэффициента b в счетчик результата 25 (декады 26 — 29), а также в память накапливающего сумматора

21. После этого устройство управления формирует импульс измерения Т,, (шина 6), который открывает ключ 30 и пропускает высокочастотные импульсы делителя частоты 15 на вход декады 10 блока формирования 9 нечетных чисел.

Делитель частоты 15 при подключении на входе его кварцевого генератора 100 кгц позволяет получить частоты в диапазоне

0 — 99999 гц с дискретностью 1 гц. Частота на выходе делителя частоты 15 равна устанавливаемому коэффициенту

1 = VК т.

Количество импульсов, поступивших на декады блока формирования 9 нечетных чисел при T,=1000 Т„, равно

Ь „= аТ„= а 1000Т„=

1000 Т,. о

Возведение этого числа в квадрат осуществляется по формуле

1+3+5+7+... + (2N — 1) =Л где N — порядковый номер нечетного числа в ряду последовательно возрастающих нечетных чисел, формируемых в блоке формирования 9 нечетных чисел.

Декада 10 последнего построена таким образом, что при поступлении счетных импульсов ее состояние соответствует нечетным десятичным числам — 1, 3, 5, 7, 9, 1, 3 и т. д.

Остальные декады 11 — 14 представляют собой обычные двоично-десятичные декады.

Таким образом, на декадах 10 — 14 при поступлении входных импульсов формируются коды последовательно возрастающих нечетных чисел.

Для образования суммы ряда нечетных чисел каждый счетный импульс на выходе ключа 30, поступающий на блок формирования 9 нечетных чисел, подается также на вход схемы временной задержки 31, на выходе которой образуется импульс «Такт суммирования», под действием которого число, содержащее в декадах 13 и 14, суммируется с числом в памяти накапливающих сумматоров

22 и 23. Полученный результат остается в памяти сумматоров 22 и 23. Временная задержка позволяет производить суммирование только по окончании переходных процессов в блоке формирования 9 нечетных чисел.

Импульсы переполнения накапливающего сумматора 21 поступают через клапан ИЛИ

33 на счетчик результата 25 (декады 26 — 29), где они суммируются с предварительно занесенным дополнительным кодом коэффициента b. После окончания импульса измерения результат измерения находится в накапливающем сумматоре 21 (младшие разряды) и в декадах 26 — 29 (старшие разряды). В дальнейшем устройство управления 5 вырабатывает импульс, который сбрасывает в нулевое состояние декады 13, 14, после чего на шине 7 вырабатывается импульс пуска канала температурной поправки 24, в котором напряжение U (с датчика температуры) преобразуется в импульс длительностью Т,. Последний подается на ключ 34, на другой вход которого поданы сигналы стабильной частоты от делителя частоты 15. Импульсы с выхода ключа 34 поступают на вход декад 13, 14, 26 — 29, где складываются с результатом измерения, Канал температурной поправки 24 представляет собой преобразователь напряжение — интервал времени. Импульс на входе блока открывает на пропорциональное входному сигналу время ключ 34, который пропускает импульсы стабильной частоты с делителя 15 на декады 13, 14 и через клапан ИЛИ

33 на счетчик 25 для суммирования температурной поправки с результатом измерения.

С целью упрощения устройства в схему включен дешифратор поправки 32, заменяю560186

Номер числа в строке

Общая сумма (результат) Сумма чисел в строке неиндицируемые разряды индицируемые разряды и/и

100

001

201

401

601

801

1001

1201

003

203

403

603

803

1003

1203

1205

197

397

597

797

997

1197

1397

130000

199

399

599

799

999

1199

1399

00001

00004

00009

00016

00036

00049

0000

5 щий по функции три разряда двоично-десятичных сумматоров и существенно более простой по конструкции, поскольку представляет собой обычную комбинационную схему, которая дешифрирует определенные состояния счетных декад 10, 11, 12. Дешифратор поправки

32 позволяет уменьшить погрешность возведения в квадрат, связанную с тем, что в суммировании не участвуют три младших десятичКак следует из таблицы, для первой сотни входных импульсов (первая строка) нужно прибавить один импульс в младший индицируемый разряд результата (сумматор 23), для второй сотни — 3 импульса, для третьей — 5 импульсов, для четвертой — 7 импульсов, для пятой — 9 импульсов.

Начиная с шестой строки по десятую, эту операцию следует повторить, поскольку содержание трех младших разрядов (декад 10, 11, 12) в следующих пяти строках повторяется, и т. д.

Единица в старшем разряде (начиная с шестой строки) образуется стократным суммированием единицы, находящейся в четвертом разряде (декада 13) блока формирования нечетных чисел, с помощью сумматора 22. Количество поправок (число добавляемых импульсов) на каждые пять строк таблицы равно 25.

Номера чисел, при которых следует вводить поправку, определяются по формуле

N< — ф 10 i, (i = 1, 2,..., 25), причем результат в правой части округляется до целого числа. Моделирование алгоритма работы прибора на ЭЦВМ «Минск — 22» показало, что погрешность возведения в квадрат пых разряда блока формирования нечетных чисел (декады 10, 11, 12) .

Сигналы поправки с выхода дешифратора поправки поступают на выход сумматора 23.

5 Принцип работы устройства с дешифратором поправки поясняется приведенной ниже таблицей, в которой сгруппированы в строки состояния декад 10, 11, 12 для каждых 100 входных импульсов. не превосходит единицы младшего разряда результата.

Формула изобретения

Цифровой прибор для частотных датчиков, содержащий последовательно соединенные формирователь, блок управления, пер35 вый ключ, элемент задержки, последовательно соединенные канал температурной поправки, второй ключ, последовательно соединенные элемент ИЛИ, счетчик, индикатор, а также синтезатор частот, включенный между вто40 рыми входами первого и второго ключей, причем второй выход блока управления соединен с входом канала температурной поправки, отличающийся тем, что, с целью повышения точности, в него дополнительно введе45 ны последовательно соединенные блок формирования нечетных чисел, дешифратор и сумматор, вторые входы которого соединены с первыми выходами блока формирования нечетных чисел, с выходом блока задержки и

50 входами счетчика, а выход — с первым входом элемента ИЛИ, второй вход которого связан с вторым выходом блока формирования нечетных чисел, входы которого соединены с выходами ключей.

560186

Корректор Н. Ау»

Редактор Е. Караулова

Заказ 1465/13 Изд. М 471 Тираж 1109 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 7К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 тх () Составитель О. Богомолов

Техред Л. Денискина