Запоминающее устройство

Иллюстрации

Показать всеРеферат

1 Ц 560258

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистимеских

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 18.07.74 (21) 2045408/24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 30.05.77. Бюллетень № 20

Дата опубликования описания 25.07.77 (51) М. Кл. G 11С 21/00

Гасударственный комитет

Совета Министров СССР оо делам изобретений и открытий (53) УДК 681.327.66 (088.8) (72) Авторы изобретения

В. П. Верижников, Б. И. Панферов и В. С. Громов

Институт электронных управляющих машин (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах с циркуляцией информации.

Известно запоминающее устройство, содержащее блоки циклической памяти (1).

1(недостаткам этого устройства относится невозможность изменения конфигурации запоминающего устройства в зависимости от характеристик хранимой информации.

s-!аиоолес олизким к изобретению является запоминающее устройство электронной клавишной вычислительной машины «Искра-Ill», содержащее блоки циклической памяти, входы которых соединены с первыми выходами соответствующих коммутаторов (2J.

1 этом устройстве затруднен выбор информационных зон, емкость которых превышает емкость одного блока циклической памяти, так как при переходе от обращения к части информационнои зоны в одном блоке циклической памяти к обращению к другой части информационной зоны в другом блоке циклической памяти создаются значительные потери времени на синхронизацию.

Цель изобретения — повышение быстродействия и информационной емкости устройства.

Это достигается тем, что в запоминающем устройстве первый вход каждого коммутатора соединен с выходом предыдущего блока циклической памяти, второй вход — с вторым выходом последующего коммутатора, второй выход — с вторым входом предыдущего коммутатора, причем выход последнего блока циклической памяти подключен к первому входу первого коммутатора, а второй вход последнего коммутатора — к второму выходу первого коммутатора.

Введение указанных связей дает возмож10 ность путем последовательного соединения близлежащих блоков циклической памяти в замкнутую цепь образовать информационную зону необходимой емкости. Дискретность изменения емкости информационных зон опре15 деляется величиной емкости одного блока циклической памяти.

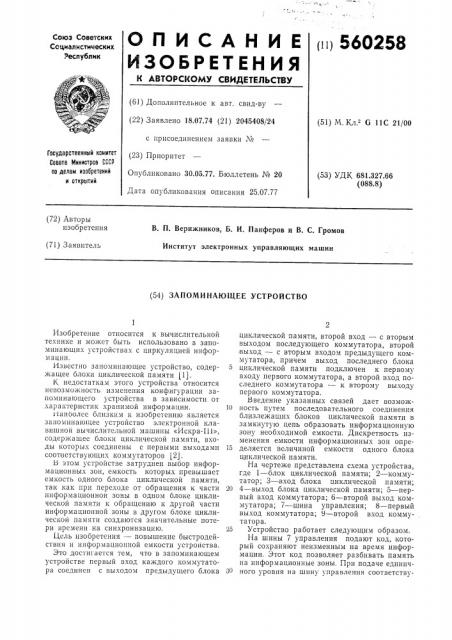

На чертеже представлена схема устройства, где 1 — блок циклической памяти; 2 — коммутатор; 3 — вход блока циклической памяти;

20 4 — выход блока циклическо"; 5 — первый вход коммутатора; 6 — второй выход коммутатора; 7 — шина управления; 8 — первый выход коммутатора; 9 — второй вход коммутатора.

25 Устройство работает следующим образом.

На шины 7 управления подают код, который сохраняют неизменным на время информации. Этот код позволяет разбивать память на информационные зоны. При подаче единич30 ного уровня на шину управления соответству560258

Составитель В. Фролов

Тсхрсд Л. Брахнина

Редактор И. Грузова

1(орректор Л. Брахнина

Заказ 1623/11 Изд. ¹ 538 Тираж 735 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ющий коммутатор обеспечивает прохождение информации на вход одноименного блока циклической памяти со своего первого входа, т. е. с выхода предыдущего блока циклической памяти. В этом случае информация с второго выхода последующего коммутатора поступает на второй выход рассматриваемого и на второй вход предыдущего коммутатора.

При приложении нулевого уровня к шине управления коммутацией соответствующий коммутатор подключает к входу одноименного блока циклической памяти информацию, поступающую на второй вход этого коммутатора с второго выхода последующего коммутатора.

Таким образом, ишрормацпонпая зона образуется последовательно расположенными блоками циклической памяти, у которых первы н комм) татор имеет нулевои уpoBellb Ha соответствующей шине управления, а все последующие коммутаторы на соответствующих шинах управлсния — единичные уровни.

Преимущество данного устройства — наличие единой стандартной цепи коммутации блоков циклической памяти, обеспечивающей прп минимальных затратах оборудования практически любой выбор информационных зон в пределах общих ресурсов памяти.

Формула изобретения

5 Запоминающее устройство, содержащее блоки циклической памяти, входы которых соединены с первыми выходами соответствующих коммутаторов, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и

10 информационной емкости устройства, в нем первый вход каждого коммутатора соединен с выходом предыдущего блока циклической памяти, второй вход — с вторым выходом последующего коммутатора, второй выход — с

15 вторым входом предыдущего коммутатора, причем выход последнего блока циклической памяти соединен с первым входом первого коммутатора, а второй вход последнего коммутатора соединен с вторым выходом первого

20 коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Friden inc. «Electronic Calcnbations, seсг111 manual», 8 — 1 — 65, США.

25 2. Техническое описание ЭКВМ «Искра-lll», завод УВМ, Орел, 1968.