Коррекционное устройство

Иллюстрации

Показать всеРеферат

О П И С А Н И Е пц 560347

ИЗОБРЕТЕНИЯ

К ABTOPCKOMV СВИДЕТЕЛЬСТВУ

Союз Советских

Социал истииеских

Республик (61) Дополнительное к авт. свид-ву 356805 (22) Заявлено 12.07.73 (21) 1942143 09 с присоединением заявки № (23) Приоритет

Опубликовано 30.05.77. Бюллетень № 20 (51) М. Кл. Н 041 1/00

Н 041 7/00

Государственный комитет

Совета Министров СССР

Ао делам изобретений и открытии (53) УДК 621.394.6 (088.8) Дата опубликования оп псаппя 30.06.77 (72) Авторы изобретения Е. В. Грязнов, В. И. Карпов, Л. М. Краков, Л. А. Марек, В. Б. Ролич и А. Г. Уваров (71) Заявитель (54) КОРРЕКЦИОННОЕ УСТРОЙСТВО

Изобретение относится к связи, в частности к устройствам передачи дискретной информации, и может использоваться в аппаратуре передачи данных, а также в электронной телеграфной аппаратуре.

По основному авт. св. № 356805 известно коррекционное устройство, содержащее задающий генератор, делитель, распределитель, запоминающий узел, входное реле, схемы совпадения, элементы ИЛИ, НЕ, управляющий триггер, три узла установки фазы, входы которых соответственно соединены с промежуточными выходами распределителя и левым плечом управляющего триггера, а выходы— с входами установки делителя (1).

Однако это устройство не обеспечивает надежной синхронизации по стартовому импульсу, подверженному влиянию дроблений.

Целью изобретения является повышение устойчивости синхронизации.

Для этого в предлагаемое коррекционное устройство введены последовательно соединенные элемент НЕ, накопитель и компаратор, на второй вход которого подано опорное напряжение, при этом к входу элемента НЕ подключен выход входного реле, а выход компаратора подключен к одному из входов соответствующей схемы совпадения.

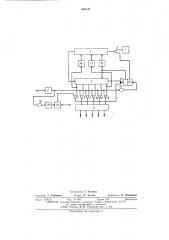

На чертеже приведена структурная электрическая схема предложенного устройства.

Коррекционное устройство содержит задающий генератор 1, делитель 2, распределитель

3, запоминающий узел 4, входное реле 5, схемы совпадения 6 — 12, элементы ИЛИ 13, HE

14, управляющий триггер 15, узлы 16, 17, 18 установки фазы, входы которых соответственно соединены с промежуточными выходами распределителя 3 и левым плечом управляющего триггера 15, а выходы — с входами ус10 тановки делителя 2, последовательно соединенные элемент НЕ 19, накопитель 20 и компаратор 21, на второй вход которого подано опорное напряжение, прп этом к входу элемента НЕ 19 подключен выход входного реле

15 5, а выход компаратора 21 подключен к одному из входов схемы совпадения 7.

Устройство работает следующим образом.

В исходном состоянии, соответствующем приему стоповой посылки, управляющий триг20 гер 15 находится в состоянии единицы. Сигналом «Единица» с левого плеча управляющего триггера 15 производится установка распределителя 3 в исходное состояние и через узел 16 по стартовой посылке — установка

25 делителя 2. Сигнал «Нуль» с правого плеча управляющего триггера 15 поступает на второй вход схемы совпадения 6, поэтому сигналы частоты задаюгцего генератора 1 через первый вход схемы совпадения 6 на вход де30 лптеля 2 не поступают. Накопитель 20 нахо560347 дится в разряженном состоянии, и с выхода компаратора 21 на вход схемы совпадения 7 поступает единица.

Прп приеме с линии стартовой посылки сигналом с выхода входного реле 5 через элемент НЕ 14 управляющий триггер 15 переводится в состояние нуль, при этом сигналом

«Единица» с правого плеча управляющего триггера 15 дается разрешение на прохождение сигналов частоты задающего генератора

1 через схему совпадения 6 на вход делителя

2. Начинается процесс деления частоты. Первый сигнал с выхода делителя 2 появляется через время, определенное исходной установкой делителя 2 с выхода узла 16. Одновременно стартовая посылка через элемент НЕ 19 поступает в накопитель 20 и далее па первый вход компаратора 21, на второй вход которого подается опорное напряжение, устанавливаемое заранее в зависимости от уровня помех.

При воздействии на накопитель 20 инвертированной стартовой lIIocbIJIIKH, подверженной влиянию дроблений, в нем за время, определяемое исходной установкой делителя 2, накапливается напряжение, равное или большее опорного. При этом на выходе комларатора

21 появляется сигнал «Нуль». Этот сигнал поступает на первый вход схемы совпадения 7.

Сигнал «Единица», появляющийся на первом выходе распределителя 3, поступает на второй вход схемы со впадения 7 и на вход узла

18. При этом сигнал на выходе схемы совпадения 7 отсутствует, управляющий триггер 15 остается в состоянии нуля и продолжается процесс формирования приемного цикла.

Сигнал «Единица» с первого выхода распределителя 3 поступает на вход узла 18, с выхода которого по кодовым посылкам устанавливается делитель 2. Время появления сигнала на втором выходе распределителя 3 определяется узлом 18. Моменты появления сигналов «Единица» на выходах с третьего по шестой распределителя 3 определяется временем 4, 24, З о, 4, где 4 — длительность кодовой посылки относительно момента поя вления сигнала «Единица» на втором .выходе распределителя 3. Сигнал «Единица» с выходов с второго по шестой распределителя 3 поступают на вторые входы схем совпадения 8 — 12.

В зависимости от состояния входного реле 5 в моменты появления сигналов «Единица» на выхсдах распределителя 3 в схемах совпадения 8 — 12 происходит совпадение или несовпадение сигналов «Единица» и и соответствии с этим запись единиц или нулей в соответствующие элементы запоминающего узла 4.

Сигнал «Единица» с шестого выхода распределителя 3 поступает также на вход узла

17 по стоповой, посылке и с его выхода — на вход установки делителя 2. Узел 17 определяет момент появления на седьмом выходе распределителя 3 сигнала «Единица», который через первый вход элемента ИЛИ 13 устанавливает управляющий триггер 15 в исходное состояние.

Сигналом «Единица» с левого плеча управляющего триггера 15 распределитель 3 устанавливается в исходное состояние и через узел 16 по стартовой посылке — делитель 2.

Цикл приема заканчивается.

Если стартовый импульс ложный, т. е. появился в результате дробления стопового импульса, то к моменту, появления импульса на первом выходе распределителя 3 напряжение на первом входе компаратора 21 меньше опорного. При этом на первом входе схемы совпадения 7 сохранится сигнал «Единица», и импульс с первого выхода распределителя

30 3 через схему совпадения 7 и второй вход элемента ИЛИ 13 устанавливает управляющий триггер 15 в состояние единица. Прп этом приемный цикл не формируется, что соответствует сигналу ложного запуска приемЗ5 ника.

Формула изобретения

Коррекционное устройство по авт. св. № 356805, отлич ающееся тем, что, с це40 лью повышения устойчивости синхронизации, введены последовательно соединенные элемент НЕ, накопитель и компаратор, на второй вход которого подано опорное напряжение, при этом к входу элемента НЕ подключен вы45 ход входного реле, а выход компаратора подключен к одному из входов соответствующей схемы совпадения.

Источники информации, принятые во внимание прп экспертизе:

50 1. ABT. св. № 356805, кл. Н 041 1/00, !971.

560347

Составитель Г. Теплова

Техред Л. Котова

Редактор Т. Рыбалова

Корректор О. Данишева

Типография, пр. Сапунова, 2

Заказ )378i15 Изд. М 493 Тираж 815 Подписное

ЦНИИПИ Государственного комитета Совета Министров CCCP по делам изобретений и открытий!

13035, Москва, jK-35, Раушская наб., д. 4/5