Устройство для контроля аналоговых параметров

Иллюстрации

Показать всеРеферат

Союз Советскин

Социалистичес»ин

Респ убли»

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВНДИТЕЛЬСТВУ

561171 (61) Дополнительное к авт. свил-ву (22) Заявлено 06.04.76(21) 2343792/24 с присоединением заявки №(23) Приоритет (43) Оиубликовано05 06 77 Бюллетень №21 (45) Дата опубликования описания04.08.77

2 (51) М. Кл.

G05 B 23/02

Государственный намнтет

Совета Мнннстров СССР оо делам нзобрвтеннй

N OTKPblTIIN (53) УДК 621.396. (088.8) (72) Автор изобретения

Г. И. Барановский (71) Заявитель (S4) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

АНАЛОГОВЫХ ПАРАМЕТРОВ

Изобретение относится к области измерения аналоговых параметров и может быть использовано в системах автоматического контроля параметров. с

Извес тно устройство.для контроля параметров, в котором измерение проводится последовательным их цсдключеннем через коммутатор к измерителю(1).

При последовательном контроле параметров из-эа сравнительно невысокого бь1стро- >р действия алектромеханических коммутаторов значительное время, затрачиваемое при измерении комплекса параметров объек та контролп, приходится на процесс коммутации, причем оно может быть сушвственно больше времени, затрачиваемого собственно на измерение. При большом числе контролируемых параметров обьекта и от раннченном времени контроля необходимо сокращать суммарное время измерения па- 20 рамвтров, Сокращение времени контропя путем введения в состав щыпаратуры контроля нескольких нэмери гелей проводит к аппаратурной избыточности; Ж

Из известных устройств наибопее бпиэ ким по технической сущности является устройство, содержащее поспедоватепьно соединенные переобраэоватепь аналог-код, блок сравнения, блок вывода и блок памяти, выход которого подкпючен ко второму входу бпока сравнения, и бпок управпепия, выходы которого подкпючены соответственно к командным входам коммутатора, бпо,ка памяти, блока сравнения и бпока вывода (2 1.

При последовательном контроле параметров после коммутации и преобразования в кодовую форму каждый контролируемый параметр сравнивается первоначально с номинальным значением, и далее результат вычитания сравнивается с полем допуска, Величины номинального значения н поля допуска считываются из блока памяти по соответствующим командам из блока упралзл ения.

Большов общее время, затрачиваемое на контроль комплекса параметров, по сравнению с суммарным временем, требуемым собственно для процесса измере56 1.171 иия, -. 6условлено инерционностью комму. тор». Г1ри этом каждому циклу измерения одного параметра предшествует процесс коммутации.

Целью изобретения является повышение быстродействия устройства.

Эта цель достигается тем, что в предложенное устройство введены трн блока вычитания, блок сложения, сумматор абсолютных величин и блок эталонных сигналов. Первые входы первого и второго блока вычитания подключены к одному иэ вьищьдов .коммутатора. Вторые входы блоков вычитания подключены к выходам блока эталонных сигналов. Первы входы третьего блока вычитания и блока сложения соединены с выходом первого блока вычитания, вторые входы - с выходом второго блока вычитания, а выходы - с входами сумматора абсолютJ ных величин, выход которого соединен со входом преобразователя аналог -код.

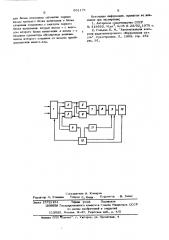

Сущность изобретения заключается в тЬм, что после сравнения в аналогDBoH форме поступающих для контроля параметров с номиницьными значениями проводится 25 их:совместное преобразование и формирование такой функции параметров, сравнением значения которой с полем допуска можно провести оценку каждого из контролируемых параметров на с оответствие обла- зО атя допустимых значений, Впок;схема )устройства приведена на чертеже.

Устройство содержит коммутатор 1 с двумя входами, выходы которого подклю- 3S чены к первым входам двух блоков 2,3 вычитания. Вторые входы последних соединены с различными выходами блока 4, эталонных сигналов, Первые входы третьего блока б вычитания и блоки 6 сложения 40 соединены с выходом первого блока 2 вычитания, вторые входя - с выходом вторэ. га.áaoaa 3 вычитания, а выходы псдклкнены ко входам сумматора 7 абсапотных величин

Выход сумматора 7 соединен со входом преобразователяя 8 аналог-код, к выходу которо»

ro подключены последовательно соединенные блок 9 сравнения и блок 10 вывода.

Второй вход блока 9 сравнения подключен к выходу блока памяти 11. Командные входы коммутатора 1, блока 4 эталонных сигналов, блока 9 сравнения, блока 10 вывбда и блока памяти 11 подключены к раздельным выходам блока 12 управления.

Устройство работает следующим образом.

После .трохождения через коммутатор 1 сигналы, характеризующие контролируемые параметры, поступают каждый на первый вход одного из блоков 2,3 вычитания, на вторые входы которых поступают аналоговые сигналы из блока 4 эталонных сигналов, величины которых равны но» минальным значениям контролируемых цараметров. Полученные на выходах блоков

2,3 вычитания две разности величин поступают на разные входы блока 6 сложения и блока 5 вычитания, с выхода которых сигналы поступают на вход сумматора

7 абсолютных величин. После суммирования результирующий сигнал поступает на вход преобразователя 8 аналог-код и затем сравнивается в блоке 9 сравнения в цифровой» форме с величиной поля допуска. Результат сравнения подается в блок 10 вывода.

Величина поля допуска считывается в блоке

9 сравнения иэ блока памяти 11. Совместная работа коммутатора 1, блока памяти 11, блока 9 сравнения, блока 4 эталонных сигналов н блок 10 вывода обеспечивается блоком

12 управления.

Последовательность операций, связанных с преобразованием контролируемых параметров, реализуемых блоками 2-7, обеспечивает. в результате получение на выходе сумматора 7 абсолютных величин такой функции контролируемых параметров, сравнением значения которой с полем допуска возможно оценить соответствие каждого иэ контролируемых параметров области допустимых значений, поэтому выход за пределы поля допуска, хотя бы одного нз контролируемых параметров, фиксируется блоком 9 сравнения.

Предлагаемое устройство позволяет существенно сократить время контроля комплекса параметров за счет уменьшения общего времени коммутации. формула изобретения

Устройство для контроля аналоговых параметров, содержащее последовательно сое« диненные преобразователь аналог-код, блок сравнения и блок вывода, блок памяти, выход которого подключен ко второму входу блока сравнения, и блок управления, выходы которого подключены к командным входам коммутатора, блока памяти, блока сравнения и блока вывода, о т и и ч а ю ш е е с я тем, что, с целью повышении быстродействия устройства, оно содержит три блока вычитания, блок сложения, сумматор абсолютных величин н блок эталонных сигналов; причем первых входы первого н второго блоков вычитания подключены к одному иэ выходов коммутатора, вторые входы блоков вычитания подключены к выхо561171

Составитель В. Комаров

Редактор Л. Утехина Техред С, еда, Корректор В. Галас

Заказ 1572/151 1 яра>к 1095 Подписное

UHHHHH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-Э5, Раун:окая наб., д. 4/5

Филиал ППП атент, r. Ужгород. ул. Проектная, 4 дам блока эталонных сигналов; первые входы третьего блока вычитания н блока сложения соединены с выходом первого блока вычитания, вторые входы - с выходом второго блока вычитания, а входы - c входами сумматора абсолютных величин, выход которого соединен со входом преобразователя анапе г-код.

Источники информации, принятые so внимание при экспертизе;

1. Авторское свидетельство СССР

% 418833, М.кл . G 05 В 23/02 1070 r.

2. Гольдин Б+ М. Автоматизация контроля радиоэлектронного оборудования су» дов, Судостроение, Л., 1968, стр. 152 рнс. 91.