Запоминающий элемент

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

l O n M C A H H E

ИЗОБРЕТЕН ИЯ (ц) 561221

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (о1) Дополнительное к авт. свид-ву— (22) Заявленс 04.01.75 (21) 2309135/24 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано 05.06.77. Бюллетень № 21 (4б) Дата опубликования описания 29.09.77 (51) У. Knf

G 11 С 11/40

Госуаа рстеенныи иомитет

Соеета Министров СССР

tto делам изобретений и открытий (53) УДК 681.327.66 (088.8} (Т2) Авторы изобретения

А. Н. Маковнй, Л. Н. Петров и В. И. Никишин (71) Заявитель (54) ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ

Изобретение относится к вычислительной технике и предназначено прежде всего для использования в оперативных запоминающих устройствах цифровых вычислительных машин, в частности, в интегральном исполнении, 5

Известен запоминающий элемент, состоящий иэ двух п-р-п транзисторов в перекрестном соединении, двух п-р-п транзисторов записи, двух инжектирующих р-п-р транзисторов, шин питания и записи.

При этом базы транзисторов в перекрестном соеди- 1п пении связаны с базами транзисторов записи, коллекторы которых подключены к объединенным базам р-п-р транзисторов, а эмиттеры — к соответ-. ствующим шинам записи, .Эмиттеры инжектйрующих транзисторов связаны с шиной питания (1) . 15

Топологически известный запоминающий элемент выполнен на вертикальных п-р-п и горизонTsJlbHbDt р-и-р транзисторах. Время, затрачиваемое на включение и выключение горизонтальных р-п-р 20 транзисторов намного больше, чем у вертикальных р-п-р транзисторов, отсюда относительно невысокое быстродействие запоминающего элемента в целом.

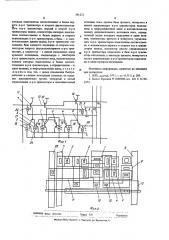

Наиоолее близким по технической сути к предложенному изобретению является запоминающий элемент, содержащий первый и второй двухколлекторный п-р-и транзисторы, соединенныв перекрестными связями, первый и второй разрешающие п-р-и транзисторы, коллекторы которых подключены соответственно к базам первого и-р-п транзистора и второго двухколлекторного,п-р-п транзистора, первый и второй п-р-п транзисторы записи, коллекторы которых подключены соответственно к базам первого и второго разрешающих н-р-п транзисторов, а базы — к соответствующим шинам записи, п-р-и транзистор считывания, база которого соединена со вторым коллектором второго двухколлекторного п-р-и транзистора, а коллектор — с шиной считывания, шину нулевого потенциала, соединенную с змиттерамн п-р-и транзисторов, источника тока, положительные полюсы которых подключены к базам соответствующих п-р-и транзисторов, а отрицательные — к шине питания, информационную шину (2).

К недостаткам этого устройства относится относительно небольшое быстродействие, обусловленtt0e указанными выше причинами, низкий фактор качества и невысокая степень интеграции. Последний недостаток обусловлен тем, что горизонтальная конструкция р-п-р транзисторов подложка не мо561221 цпНИПИ Заказ 1581/154

Тираж 729

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 которых подключены соответственно к базам первого п-р-и транзистора и второго двухколлекторйого п-р-п транзистора, первый и второй п-р-и транзисторы записи, коллекторы которых подключены соответственно к базам первого и второго разрешающих п-р-и транзисторов, а базы — к соответствующнМ щи@ам залнсн, п-р-и транзистор считывания, база которого соедынеяв со вторым коллектором, второго двухколлакториого и-р-ц транзистора, а коллектор — с шиной:ечнтывання, шину нулевого потенциала, соединенную с эмиттером п-р-п транзисторов, источники тока, положительные полюсы которых подключены к базам соответствующих л.р-п транзисторов, а отрицательные — к шине питания, и информационную шину, о т л и ч а-. ю щи йс я тем, что, с целью повышения быстродействия н степени интеграции элемента, он содержит дополнительно третий, четвертый и пятый управляющие и-р-п транзисторы и дополнительньш источник тока, причем базы третьего, четвертого и пятого управляющих и-р-п транзисторов подклю. чены к информационной шине и положительному полюсу дополнительного источника тока, отрицвтелъныи полюс которого подключен к шине пита ння, коллекторы третьего и четвертого управляю щнх п-р-и транзисторов подключены соответствен. но к коллекторам первого н второго п-р-п транзисторов записи,. коллектор пятого управляющего

1О п-р-п транзистора подключен к базе п-р-п транзистора считывания, а эмиттеры третьего, четвертого и пятого управляющих п-р-и транзисторов подключены к шине нулевого потенциала.

Источники информации, принятые во внимание прн экспертизе:

1. ИЬ1,,;.1, Ю1, -.--cc-б, V S, ð. 28З.

2. П1атент Фракщти К 2088388, кл. 611 С 11/40,.

1972.