Формирователь импульсов для управления диодными фазовращателями

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнх

Социалистических

Республик

<»I 562934 (61) Дополнительное к авт. свпд-ву— (22) Заявлено 26.11.75 (21) 2192767/21 с присоединением заявки— (23) Приоритет— (43) Опубликовано 25.06.77. Бюллетень \Ъ 23 (45) Дата опубликования описания 14.09.77 (51) М. Кл.- Н 03 К 5, 01

Государственный комнтет

Совета Мнннстров СССР по делам изобретений н аткрытнй (53) УДК 621.374.38 (088.8) (72) Авторы изобретения

М. С. Любчанский и А. А. Пиотровский

1 (71) Заявитель (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ

ДЛЯ УПРАВЛЕНИЯ ДИОДНЫМИ ФАЗОВРАЩАТЕЛЯМИ

Изобретение относится к импульсной технике и может быть использовано в технике антенных фазированных решеток с электрическим сканированием луча для формирования импульсов управления диодными фазовращателями.

Известны формирователи импульсов, которые могут быть использованы для формирования импульсов управления диодными фазовращателями.

В качестве одной из возможных схем для формирования импульса управления в кахкдом разряде фазовращателя может быть рассмотрена схема с отдельным ключевым каскадом, например, на одном транзисторе, управляемом по входу от логической схемы, соответствующей данному разряду. Разрядный диод фазовращателя подключен к выходу ключевого каскада и при открывании последнего обеспечивается протекание требуемого -.ñêà прямого смещения через диод соответствующего разряда фазовращателя. Выход ключевого каскада через резистор подключен также к источнику обратного смещения для диода фазовращателя. При выключении ключевого каскада обратное напряжение смещения оказывается поданным на диод фазовращателя (1).

Недостатком такой схемы является низкое быстродействие и большая потребляемая З0 мощность при попытке увеличения быстродействия за счет уменьшения величины резистора в цепи обратного смещения диода фазовращателя, что необходимо делать для уменьшения постоянной времени цепи разряда выходной цепи ключевого каскада.

Известен также формирователь импульсов для управления дподными фазовращателями, в котором на каждый разряд фазовращателя используется транзисторно-диодный формироBàòåëb, управляемый от соответствующего разрядного логического элемента. Формирователь импульсов содержит ключевой каскад, на одном транзисторе выход которого подключен к выходу соответствующего логического элемента управления этим каскадом, вход которого соединен с соответствующей шиной входного сигнала. Эмпттерная цепь каскада соединена с источником прямого смещения диодом фазовращателей, а коллекторная цепь подсох »1нена через резистор к источнику обратного смещения диодов фазовращателей и к первому электроду дополнительного диода, параллельно которому подклю сн переход база — эмиттер кл1очевой схемы, коллектор которой также подкл10чен к и=то-I;II»;i обратного смещения диодов фазовращателей, прп этом второй электрод дополнительного диода подключен к разрядному диоду фазовращателя (2).

Однако известный формирователь требует логическую схему, два транзистора и диод на каждый разряд фазовращателя. Кроме того, для обеспечения быстрого запирания диодов фазовращателя, т. е. высокого быстродействия, требуется достаточно большой разрядный ток от транзистора в цепи запирания, а для его обеспечения — большой ток в базе этого транзистора. Ток базы задается через резистор от источника запирающего напря>кения, TBK как запирающий транзистор включен по схеме с общим эмиттером. При открывании кгпочевого каскада на этом резисторе выде7ÿñòñÿ достаточно большая мощность.

Вместе с тем быстродействие указанной схемы также недостаточно, так как срабатывание запирающего диод фазоврашателя транзистора происходит после запирания транзистора ключевого каскада и разряда пар азитной емкости в его коллекторной цепи (через достаточно большой для уменьшения рассеиваемой мощности резистор в цепи обратного смещения) до напряжения, открывающего транзистор запирания. Все это вызывает задержку в срабатывании схемы, снижает ге быстродействие.

Кроме того, в указанной схеме через дополнительный диод протекает прямой ток диода фазовращателя, что требует увеличенияя напр".!кения питания для прямого смещения диодов фазовращателя и является дополнитеяы!Ым дестаб1!лизир1!Ощим QBI

Целью изобретения является повышение быстродействия формирователя импульсов для управления диодными фазовращатсля IH.

Для этого в формирозатель импульсов для управления диодными фазсврашателямп, содержащий ключевые каскады, например, на транзисторах p — n — р типа, базовый вход ка>кдого из которых подкл!очен к выходу соответствуюц;его логического элгмгнта управления этим каскадом, один из входов каждого логического эл-.ìåíòà соединен с соответству!ошей шиной ные цепи каскадов соединены с источником прямого смещения диодов фазоврашат"лгй, B коллекторные цепи по тсоединены к анодам диодов фазовращателей и через резисторы соединены с источником обратного смещения этих диодов, введены логи !сский элемент управления запиранием диодных фазовра;цатглей, вход которого соединен с допо7HHTeльнсй шиной управления, а один выход подключен ко вторым входам логических э,7гме!1тов управления ключевыми каскадами, разделительные диоды и дополнительный ключевой каскад на транзисторе, например, типа !

1 — р — а, эмиттер которого соединpH с источником обратного смещения диодов фазовращателя, базовая цепь соединена со вторым выходом упомянутого дополнитгльногс элемента управления запиранием, а коллекторная цепь через разде 7итгльныг дилэдь! подключена к анодам диодов фазоврашгтелей.

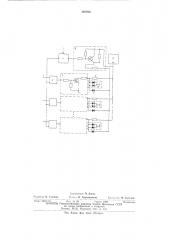

На чертеже приведена с. ма формирозатгля импульсов для управления дисдными фазовр ащателями.

Фосмирователь имеет первый вход 1 логичгских элемгнTQB 2 управления ключевыми каска ами 8, например, на транзисторах типа р — и — p, соединенный с соответствующей шиной входного сигнала. Вторые входы логических элементов 2 управления ооъедииены и подключены к первому выходу логического элгх10HTB 4 1 п13авлгния запl!ран!!ем диодных фазозращателей. Вход логического элемента

4 соединен с дополнительной шиной упразления. Коллекторные цепи ключевых каскадов

3 подсоединены через резисторы 5 к источнику б обратного смещения диодов фазовращатгля. Разделительные диоды 7 одними элек20 тродамп подключгны к коллекторHI I.;I цепям ключевых каскадов 8. Вторые электроды диодов 7 объединены и подключены к коллек—.орной цепи дополнительного ключевого каскада 8, например, на транзисторе типа

25 и — р — и. Базовая цепь ключевого KBcI

З5 ссответству!оших диодов фазов",".шателгй, вторые электроды которы.; подключены к оби;ей ши..е источников прямого и обратного смешения эти.; диодов. В момент подачи вход ого управляющего сигнала логические

40 элементы 2 управления в соответствии со значениями сигналов управления либо откры3 .:loT, либо запирают соответству!ощиг ключ"-вые каскады 8. При этом через диоды 9 .,.азов;IB."öBTå låII через откпь1ть!е .;.".!очень!c каскады 3 протекают токи прямого смещения, обеспечивающие требуе.

В предлагаемом устройстве для повышения быстродействия в момент смены упсавляющих сигналов на входы логнчески_#_ элементов 2 управления и ключевой схемы 8 по60 дается коротки!1:1мпульс от схемы 4.

Прп этом все ключевые каскады 8 на указанный отре301 все.;101!и заг ;раются и ток ими от истсчник". б нг потребляется. Тогда через ключсвуio схему 8 ст источника б через небольшое внутреннее сопротивление схе562914 мы 8 происходит obIcTpOà запирание диодов

9 (пока напряжение на выходе ключевой схемы 3 за " ÷åò .паразитных параметров остается меньше напряжения источника 6) .

По окончании выдержки расчетного времени (по наихудшим разбросам параметров схем) короткий импульс со схем 2 и 8 снимается и ключевые каскады 3 устанавливаются в состояние в соответствии с поданным измененным входным кодом. Таким образом, быстродействие схемы определяется временем короткого импульса схемы 4 и временем нарастания тока в диодах 9 от момента включения входного сигнала (которое много меньше времени спада) до момента обеспечечия запирающего потенциала на диодах.

Может быть получено достаточно высокое быстродействие схемы, так как ток, подаваемый на рассасывание паразитных емкостей и накопленного заряда диодов фазовращателя, может быть выбран большим. Следовательно, постоянная времени цепи запирания оказывается очень малой. Это возможно, так как схема по потреблению тока через ключевую схему 8 от источчика 6 подключается на короткое время и при включении ключевых каскадов 8 ток ключевой схемой 8 вообще не потребляется.

Предлагаемая схема псзволяет не только уменьшить потребление тока, но и уменьшить требуемое оборудование на разряд фазовращателя до одного транзистора и в ключевом каскаде и одного разделительного диода, так как дополнительный ключ 8 может быть одним на фазовращатель (на все разряды) либо даже на группу фазовращателей.

Для уменьшения времени рассасывания схемы 8 целесообразно общую точку диодов

7 в ключе 8 подключить к источнику 6 сбратного смещения диодов 9, так как при этом не требуется перезаряд паразитных емкостей самой ключевой схемы 8 при ее выключении.

Предлагаемая схема допускает перекрытие во времени момента начала запирания ключевых каскадов 8 коротким импульсом с моментом включения схем 8, если транзисторы рассчитаны по току. Кроме того, в отличие от прототипа предлагаемая схема не содержиг в цепи прямого смещения диодов фазc0"..àùателя каких-лисс другиx. диодов.

Так1гм ооразом, предлагаемый формирователь 11. пульсов 1ля управления диоднымн фазОВращателями ОоеспечпВает Высокое быстродействие, малое потребление энергии, достаточно простую схему реализации.

Формула изобретения

Формирователь импульсов для управления диодными фазовращателямп, содержащий ключевые каскады, например, на транзисторах р — n — р типа, базовый вход каждого пз которы.; подкл1очен к выходу соответствующего логическогс элемента управления этим ка кадом, Один пз ВходоВ каждого логического элемента соединен с соответствующей шиной входного сигнала, эмиттерные цепи кас20 кадов соединены с источником прямого смещения диодов фазовращатслей, а коллек;-орные цепи подсоединены к анодам диодов фазовращателей и через резисторы соединены с истсчником обратного смешения этих

Б «Одов, отличающ ийся тем, что, с целью новь|щения быстродействия, в него введены логический элемент управления запцранием диодных фазовращателей, вход которого соеди ен с дополнительной шиной управления, а

З0 Один выход подключен ко вторым входам ло-ически элементов управления ключевыми каскадами, разделительные диоды и дополнительный ключевой каскад Hà транзисторе, например, типа и — p — и, эмиттер которого соединен с источником обратного смещения диодов фазовращателя, базовая цепь соединена со вторым выходом упомянутого дополнительного элемента управления запиранием, а коллекторная цепь через разделительные дио40 ды подключена и анодам диодов фазовращателей.

Источники информации, принятые во внимание прп экспертизе.

45 1. Ицхоки Я. С., Овчинников Н. И. Импульсные и цифровые устройства. М., «Советское радио», 1973, с. 200, рис. 33.

2. IEFE Тгапвас11О1,МТТ-22, 1974, М 6, ". 668. фиг. 10, а.

562914! (орректср И. Симкина

Редактор О. Степина

Заказ 535/!-!!! Изд. ¹ 80 I t t!) àæ 080 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 7К-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент»

Ц (I(!!з

Составитель П. Лягни

Текред If. !(арандашова