Устройство временной коммутации

Иллюстрации

Показать всеРеферат

О П И С А Н И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистимеских

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 17.12.75 (21) 2303398/09 с присоединением заявки № (23) Приоритет

Опубликовано 30.06.77. Бюллетень № 24

Дата опубликования описания 15.07.77 (51) М. Кл 2 H 04J 3/00//

Н 04@ 1/52

С есударственный комитет

Вееета Министров СССР по делам изобретений и аткрмтии (53) УДК 621.395.345 (088.8) (72) Автор изобретения

Н. И. Витиска (71) Заявитель

Таганрогский радиотехнический институт им. В. Д. Калмыкова (54) УСТРОЙСТВО ВРБМБИНОЙ КОММУТАЦИИ

Изобретение относится к технике связи и может использоваться в вычислительных системах, а также в электронных автоматизированных телефонных станциях.

Известно устройство временной коммутации, содержащее первый распределитель, выходы которого подключены к входам блока памяти и управляющим входам fL клточей, на сигнальные входы которых поданы информационные сигналы, а выходы и ключей соединены с сигнальным входом общего ключа, выход которого подключен к сигнальным входам и дополнительных ключей, управляющие входы которых соединены с выходами второго распределителя, к первому входу которого подкл:очен выход элемента ИЛИ, первый вход которого соединен с первым входом первого распределителя, а на второй вход элемента ИЛИ подан сигнал запуска.

Однако известное устройство не обладает достаточным быстродействием.

Цель изобретения — повышение быстродействия.

Для этого в устройство временной коммутации, содержащее первый распределитель, выходы которого подключены к входам блока памяти и к управляющим входам и ключей, на сигнальные входы которых поданы ичформационные сигналы, а выходы и ключей соединены с сигнальным входом общего ключа, выход которого подключен к сигнальным входам и дополнительных ключей, управляющи, входы которых соединены с выходами вторсго распределителя, к первому входу которого подключен выход элемента ИЛИ, первый вход которого соединен с первым входом первого распределителя, а на второй вход элемента

ИЛИ подан сигнал запуска, введены элемент

И, два одновибратора, вьтчитающий счетчик и многовходовой элемент И, входы которого соединены с нулевыми выходами разрядов вычитающего счетчика, а первый выход — с управляющим входом общего ключа и входом первого одновибратора, выход которого подключен к первому входу первого распределителя, прп этом выходы блока памяти соединены с единичными входами разрядов вычитающего счетчика, счетный вход которого соединен с вторым входом второго распределителя и выходом элемента И, первый вход которого подключен к второму выходу многовходового элемента И и к входу второго одновибратора, выход которого соединен с третьим входом второго распределителя, причем выход эле25 мента ИЛИ соединен с соответствующим входом вычитающего счетчика, а на второй вход элемента И поданы тактовые импульсы.

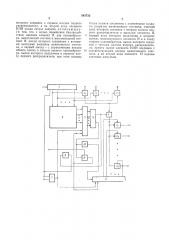

На чертеже представлена структурная электрическая схема устройства временной комму39 тации.

563732

Устройство содержит первый распределитель 1, выходы которого подключены к вхо",ам блока 2 памяти и к управляющим входам ключей Зь 3, ...,3, на сигнальные входы которых поданы информационные сигналы, а выходы ключей Зь 32, ...,3 соединены с сигнальным входом общего ключа 4, выход которого подключен к сигнальным входам дополнительных ключей 50 5г,...,5 . Управляющие входы ключей 5 соединены с выходами второго распределителя 6, к первому входу которого подключен выход элемента 7 NEIN, первый вход которого соединен с первым входом первого распределителя 1, а на второй вход элемента 7 ИЛИ подан сигнал запуска. Кроме того, устройство содержит элемент 8 И, два одновибратора 9 и 10, вычитающий счетчик 11 и многовходовый элемент 12 И, входы которого соединены с нулевыми выходами разрядов вычитающего счетчика 11, а первый выход— с управляющим входом общего ключа 4 и входом первого одновибратора 9, выход которого подключен к первому входу первого распределителя 1. При этом выходы блока 2 памяти соединены с единичными входами разрядов вычитающего счетчика 11, счетный вход которого соединен с вторым входом второго распределителя 6 и выходом элемента 8 И, первый вход которого подключен к второму выходу многовходового элемента 12 И и к входу второго одновибратора 10, выход которого соединен с третьим входом второго распределителя 6. Выход элемента 7 ИЛИ соединен с соответствующим входом вычитающего счетчика 11, а на второй вход элемента

8 И поданы тактовые импульсы.

Устройство временной коммутации работает следующим образом, После подачи сигнала запуска на второй вход элемента ИЛИ в устройстве происходит установка в нулевое состояние по соответствующему входу вычитающего счетчика 11 и второго распределителя 6 и запись логической единицы в первый распределитель 1. В первом распределителе 1 возбуждается первый выход, который открывает ключ 3r и формирует сигнал на первом входе блока 2 памяти.

На выходах блока 2 памяти образуется первый адрес исходящей линии, которая по программе должна быть скоммутирована с первой входящей линией устройства. Сформированный адрес записывается в вычитающий счетчик 11, С этого момента на втором выходе многовходового элемента 12 И появляется единичный потенциал, который поступает на входы элемента 8 И и второго одновибратора 10. На выходе второго одновибратора 10 формируется импульс, запись которого производится во второй распределитель 6 через его третий вход. Тактовые импульсы, поступающие на второй вход элемента 8 И, пройдя через открытый элемент 8 И, поступают на счетный вход вычитающего счетчика 11 и второй вход второго распределителя 6. В вычитающем

25 зо

65 с .етчпкс 11 с приходом каждого тактирующего импульса записанный адрес исходящей линии уменьшается на единицу. Соответственно во втором распределителе 6 происходит сдвиг логической единицы на один разряд и последовательное возбуждение его выходов. Одновременно с этим на управляющих входах допо".rrèòåëürrûõ ключей 50 5>, ..., 5„формируются сигналы, которые последовательно открывают данные ключи.

Когда в вычитающем счетчике 11 образуется нулевой код, то на первом выходе многовходового элемента 12 И формируется единичный потенциал, а на его втором выходе— нулевой потенциал. Единичный потенциал открывает общий ключ 4, а нулевой потенциал закрывает элемент 8 И и тем самым останавливает сдвиг во втором распределителе 6.

Также прекращается и подсчет импульсов в вычнтающем счетчике 11. В этот момент потенциалом с выхода второго распределителя

6 открывается тоелько заданный дополнительный ключ 5 и тем самым через открытые так>ке ключи Зr и 4 образуется первый соединительный путь мехкду входящей линией и соответствующей исходящей линией.

Второй соединительный путь в устройстве для входящей и соответствующей исходящей линии образуется аналогичным образом только после того, как сигналом с выхода первого одновибратора 9 с задержкой производится сдвиг единицы в первом распределителе 1 и через элемент 7 ИЛИ сброс в нулевое состояние вычитающего счетчика 11 и второго распределителя 6. В первом распределителе 1 возбужден только второй выход, сигнал с коTopoI открывает ключ 32 и формирует на выходах блока памяти 2 адрес той исходящей линии, которая по программе должна быть скоммутирована с этой входящей линией.

Следовательно, сдвигая последовательно единицу в первом распределителе 1, за и шагов выполняется вся программа коммутации, записанная в блоке памяти 2. При этом на каждый шаг требуется число тактов, совпада1ощее с номером исходящей линии, которая коммутируется в этом шаге.

В предложенном устройстве временной коммутации быстродействие повышается в 2 раза по сравнению с известным.

Формула изобретения

Устройство временной коммутации, содержащее первый распределитель, выходы которого подключены к входам блока памяти и к управляющим входам и ключей, на сигнальные входы которых поданы информационные сигналы, авы,ходы и ключей соединены с сигнальным входом общего ключа, выход которого подключен к сигнальным входам и дополнительных ключей, управляющие входы которых соединены с выходами второго распределителя, к первому входу которого подключен выход элемента ИЛИ, первый вход которого соединен с первым входом первого распределителя, а на второй вход элемента

ИЛИ подан сигнал запуска, о т л и ч а ю щ е еся тем, что, с целью повышения быстродействия, введены элемент И, два одновибратора, вычитающий счетчик и многовходовой элемент И, входы которого соединены с нулевыми выходами разрядов вычитающего счетчика, а первый выход — с управляющим входом общего ключа и входом первого одновибратора, выход которого подключен к первому входу первого распределителя, при этом выходы блока памяти соединены с единичными входами разрядов вычитающего счетчика, счетный вход которого соединен с вторым входом второго распределителя и выходом элемента И, первый вход которого подключен к второму выходу многовхолового элемента И и к входу второго одновибратора, выход которого соединен с третьим входом второго распределителя, причем выход элемента ИЛИ соединен с

1О соответствующим входом вычитающего счетчика, а на второй вход элемента И поданы тактовые импульсы.