Многоканальное устройство синхронизации

Иллюстрации

Показать всеРеферат

нц 563733

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 17.02.70 (21) 1404510, 09 с присоединением заявки № (23) Приоритет

Опубликовано 30.06.77. Бюллетень ¹ 24

Дата опубликования описания 15.07.77 (51) М. Кл.-" Н 04J 3, 06

Н 04L 7/02

Государственный комитет

Совета Министров СССР па делам изобретений н открытий (53) УДК 621.394.662 (088.8) (72) Авторы изобретения

T. P. Яфетас, Е. Ф. Дещиц, С. И. Сидарас, А. В. СаснаускаТ и Г. Б. Кан

Специальное конструкторское бюро вычислительных машин (71) Заявитель (54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО СИНХРОНИЗАЦИИ

Изобретение относится к устройствам синхронизации работы систем при обмене информацией между ними и может использоваться в центральном устройстве вычислительной машины для обеспечения его синхронной работы с периферийными устройствами.

Известно многоканальное устройство синхронизации, содержащее формирователь тактовых синхроимпульсов и блок канальных импульсов циклового фазирования (1).

Однако в известном устройстве отсутствует возможность обмена информацией со станциями, работающими с разной тактовой частотой, а также наличие случайной рассинхронизации системы в ходе ее работы приводит к потерям времени для восстановления синхронизма.

Цель изобретения — сокращение времени вхождения в синхронизм при переключении каналов.

Для этого в многоканальном устройстве синхронизации, содержащем формирователь тактовых синхроимпульсов и блок канальных импульсов циклового фазирования, введены последовательно соединенные коммутатор канальных импульсов циклового фазирования, блок управления и коммутатор канальных задающих импульсов, включенные между выходами блока канальных импульсов циклового фазирования и входом управления формирователя тактовых синхроимпульсов, причем второй выход блока управления подключен к входу управления коммутатора канальных импульсов циклового фазирования, на соответствующий вход блока управления подан сигнал «Переключение каналов», а один из выходов формирователя тактовых синхроимпульсов соединен с вторым входом блока управления.

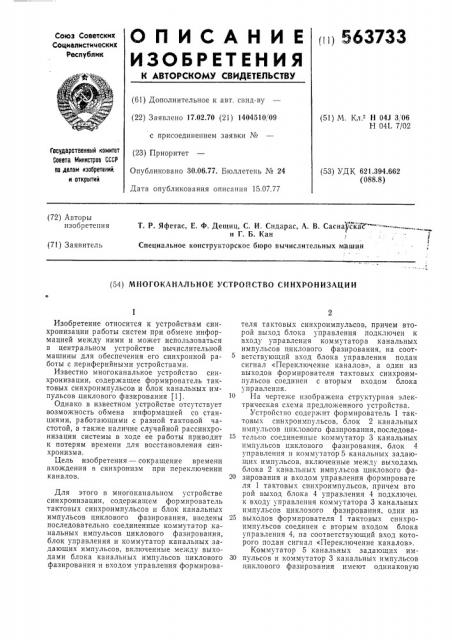

1О На черте>ке изображена структурная электрическая схема предложенного устройства.

Устройство содержит формирователь 1 тактовых синхроимпульсов, блок 2 канальных импульсов циклового фазирования, последова15 тельно соединенные коммутатор 3 канальных импульсов циклового фазирования, блок 4 управления и коммутатор 5 канальных задающих импульсов, включенные между выходамк блока 2 канальных импульсов цпклового фа20 зирования и входом управления формировате ля 1 TBKTQBbIx синхроимпульсов, причем вто рой выход блока 4 управления 4 подключен к входу управления коммутатора 3 канальных импульсов циклового фазирования, один из

25 выходов формирователя 1 тактовых синхроимпульсов соединен с вторым входом блока управления 4, на соответствующий вход которого подан сигнал «Переключение каналов».

Коммутатор 5 канальных задающих имЗО пульсов и коммутатор 3 канальных импульсов

IIHI<;IoB0I фазирования имеют одинаковую

563733 структуру и состоят из дешифраторов 6 и 7 соответственно, соединенных своими выходами с элементами И 8 и И 9, число которых соответствует числу периферийных устройств, вы. оды этих элементов подключены к элемен-.ам ИЛИ 10 и ИЛИ 11 соответственно.

Блок управления 4 содержит регистр 12, соединенный своим выходом с элементом И 13 и блоком 14 для фиксирования поступления сигнала в регистр 12. Блок 14 своим выходом соединен с элементом И 15, другой вход которого соединен с выходом формирователя 1, а выход — с регистром 16 и триггером 17.

Единичный выход триггера 17 соединен с элементом И 18. Другой вход элемента И 18 соединен с выходом элемента ИЛИ 10, а выход — с элементом И 13 и через линию за.",ержки 19 с нулевым входом триггера 17 и с регистром 12. Выход элемента И 13 подключен к регистру 16, выход которого соединен с д".пифратором 7.

Входы коммутатора 5 и блока 2 канальных импульсов циклового фазирования 2 соедине, ы с каналами 20-1 — 20-и (всего и каналов) задающих импульсов, соединенными с и периферийными устройствами (на чертеже не показаны).

Устройство работает следующим образом.

При наличии в регистре 16 информации, представляющей определенное периферийное Зо устройство, на соответствующем выходе дешифратора 7 имеется сигнал, разрешающий проход через определенный элемент И 9 серии зада|ощих импульсов, поступающей от данного периферийного устройства. Серия задаю- 35 щих импульсов через элемент ИЛИ 11 поступает па вход управления формирователя 1 тактовых синхроимпульсов и тем обуславливает синхронную его работу с формировате..ем 1 тактовых синхроимпульсов данного пе- 40 рпферийного устройства, управляемым той же серией задающих импульсов. При потребности переключиться на синхронную работу с другим периферийным устройством информация о том, к какому устройству следует переключиться, записывается в регистр 12 сигналом «Переключение каналов». Блок 14 для фиксирования поступления сигнала в регистр

12 при этом выдает сигнал на элемент И 15.

1(огда на другой вход элемента И 15 поступ" ñò сигнал с формирователя 1, означающий, что в данный момент центральное устройство находится в состоянии, допускающем приостановление его работы, сигнал, возникший на выходе элемента И 15, гасит регистр

1б. Этим обуславливается отсутствие сигна"..а на всех выходах дешифратора 7, вследствие чего на вход формирователя 1 не поступает никакая серия задающих импульсов и формирование тактовых синхроимпульсов пре- 60 краша ется.

Сигнал с выхода элемента И 15 также поступает на триггер 17 и устанавливает его в единичное состояние. Единичный сигнал триггера 17 поступает на вход элемента И 18. 65

В соответствии с содержанием регистра 12 на одном из выходов дешифратора 6 возникает сигнал, поз|олчющий проход через один из элементов И 8 канальных импульсов фазирования соответствующего периферийного устройства, сформированных блоком канальных импульсов циклового фазирования 2 из серии задающих импульсов этого периферийного устройства и означающих, что в момент поступления импульса фазирования фаза цикла тактовых синхроимпульсов периферийного устройства находится в состоянии, допускающем начало синхронной работы с центральным устройством. Импульсы циклового фазирования через элемент ИЛИ 10 поступают на элемент И 18. При наличии на другом входе элемента И 18 единичного сигнала триггера

17 выходной сигнал элемента И 18 разрешает проход содержания регистра 12 в регистр 16.

Это означает подключение входа управления формирователя 1 к каналу задающих импульсов периферийного устройства, определенного содержанием регистра 16. Сигнал с выхода элемента И 18 также поступает через линию задержки 19 на нулевой вход триггера 17 и на регистр 12. При этом триггер 17 и регистр

12 гасятся. Это подготавливает устройство синхронизации к принятию сигнала «Переключение каналов», задающего следующее переключение каналов.

Функцию блока 2 канальных импульсов циклового фазирования могут выполнять блоки формирования тактовых синхроимпульсов периферийных устройств, если соответствующие их выходы подключить к входам коммутатора 3. Целесообразность использования одного или другого варианта зависит от расстояния периферийных устройств от центрального устройства.

Формула изобретения

Многоканальное устройство синхронизации, содержащее формирователь тактовых синхроимпульсов и блок канальных импульсов циклового фазирования, о т л и ч а ю щ е е с я тем, что, с целью сокращения времени вхождения в синхронизм при переключении каналов, введены последовательно соединенные коммутатор канальных импульсов циклового фазирования, блок управления и коммутатор канальных задающих импульсов, включенные между выходами блока канальных импульсов циклового фазирования и входом управления формирователя тактовых синхроимпульсов, причем второй выход блока управления подключен к входу управления коммутатора канальных импульсов циклового фазирования, на соответствующий вход блока управления подан сигнал «Переключение каналов», а один из выходов формирователя тактовых синхроимпульсов соединен с вторым входом блока управления.

Источники информации, принятые во внимание при экспертизе

1. Патент США Хо 3230309, кл. 178-53, 966.

563733

Составитель Е. Погиолов

Техред М. Семенов

Корректор H. Аук

Редактор Е. Дайн

Типография, пр. Сапунова, 2

Заказ 1544/17 Изд. № 564 Тираж 818 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5