Устройство для контроля многоканальной системы связи с временным разделением каналов

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 11ц 563734

ИЗО БРЕТ ЕН И Я

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. cBIiä-ву (22) Заявлено 08.12.74 (21) 2081696/09 с присоединением заявки № (23) Приоритет

Оп .бликовано 30.06.77. Бюллетень j¹ 24 (51) il, Кл, - H 0-1J 3/14 /

Н 04J 3/06

Гааударственнь и камитет

Совета Министрае СССР па делам изааретений и аткрытий (53) УДК 621.395.4:681..327.8 (088.8) Дата опубликования описания 23.07.77 (72) Авторы изобретения

Л. Н. Оганян и Л. Д. Колыхалов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МНОГОКАНАЛЪНОЙ

СИСТЕМЫ СВЯЗИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ

Изобретение относится к технике связи и может использоваться в многоканальных системах связи с временным разделением каналов.

Известно устройство;ля контроля многоканальной системы связи с временным разделением каналов, содержащее на передающей стороне генератор контрольной информации, синхронизаторы, контрольные выходы которых подключены и блоку управления стаффингом, соответствующие выходы которого соединены с управляющими входами синхронизаторов и входом блока цикловой синхронизации, выход которого, а также информационные выходы синхронизаторов и управляющий выход блока управления стаффингом подключены к соответствующим входам передающего коммутатора, а на приемной сторо»е — приемник контрольной информации, приемный коммутатор, выходы которого подключены к соответствующим входам десинхронизаторов, блока управления стаффннгом и блока цикловой синхронизации, выходы которого соединены с синхронизирующими входами десинхронизаторов и блока управления стаффингом, выход которого соединен с управляю;цими входами десинхронизаторов ,j1J.

Однако известное устройство имеет невысокую точность контроля.

Цель изобретения — повышение точности контроля.

Для этого в устройстве для контроля многоканальной системы связи с временным раздс5 лением каналов, содержащем на передающей стороне генератор контрольной информации, спнхроннзаторы, контрольные выходы которых подключены к олок, 1 IIp33ëeíèÿ стаффингом, соответствующие выходы которого

10 соединены с управляющими входамп синхронизаторов и входом блока цпкловой синхронизации, выход которого, а также информационные выходы синхронизаторов и управляющий выход блока управления стаффннгом

15 подключены к соответствующим входам передающего коммутатора, а на приемной стороне — приемник контрольной информации, приемный коммутатор, выходы которого подклю чены к соответствующим входам десннхрони20 заторов, блока управления стаффпнгом и блока цикловой сийхронизации, выходы которого соединены с син: ронизпрующимн входамп десинхронизаторов и 0лока управления стаффингом, вы. од которого соединен с управ25 ляющими входами десин. ронизаторов, на передающей стороне доголнитсльныи выход олока управления стаффпнгом подключен к входу генератора контрольнон информации, выход которого подключен к дополнительным

30 входам синхронизаторов, а на приемноп сто563734 роне дополнительный выход блока управления стаффингом подключен к одному из входов приемника контрольной информации, к другому входу которого подкл1очены дополнительныс выходы десинхронизаторов. Приемник контрольной информации может быть выполнен, например, в виде последовательно соединенных входного блока сравнения, накопителя и счетчика.

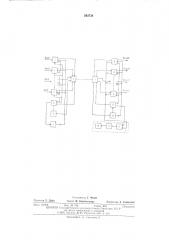

1-1а чертеже изобра:кена структурная схема предложенного устройства.

Устройство для кснтро. Iя мнoг0кàнnëüttoé системы связи с временным разделением каналов содержит на передаю;цей стороне генератор 1 контрольной информации, синхронизаторы 2, ко:1трольные выходы которы. подключены к блоку 3 управления стаффингом, блок 4 цикловой синхронизации, псредаю1ций коммутатор 5, а на приемной стороне — приемник б контрольной информации, приемный коммутатор 7, выходы которого подключены к соответствующим входам десин. ронизаторов 8, блока 9 управления стаффингом и блока 10 цикловой синхронизации. Приемник б контрольной ин1формации состоит из последовательно соединенных входного блока 11 сравнения, накопителя 12 и счетчика 13. Выходы блока 3 управления стаффингом соединены с управляющими входа ми синхронизаторов 2 и входом блока 4 цикловой синхронизации, выход которого, а так ке информационные выходы синхронизаторов 2 и управляющий выход блока 3 управления стаффингом подключены к соответствующим входам переда1ощего коммутатора 5. Выходы блока

10 цикловой синхронизации соединены с синхронизирующими входами десинхронизаторов

8 и блока 9 управления стаффингом, выход которого соединен с управляющими входами десинхронизаторов 8. На передающей стороне дополнительный выход блока 3 управлсния стаффингом подключен к входу генератора 1 контрольной информации, выход которого подключен к дополнительным входам синхронизаторов 2. На приемной стороне дополнительный выход блока 9 управления стаффингом подключен к одному из входов приемника б контрольной информации, к другому входу которого подключены дополнительные выходы дссинхронизаторов 8.

Предложенное устройство работает следующим образом.

Синхронизаторы 2 по существу представляют собой устройства памяти, заппсь в которые происходит с тактовой частотой входящего цифрового потока, а считывание — с тактовой частотой, определяемой местным генераторным оборудованием, причем частота считывания несколько выше частоты записи.

Для выравнивания скоростей в синхронизаторах 2 в информационную последовательность вводятся балластные тактовые интервалы.

Все синхронизаторы 2 работают одинаково, поэтому работа устройства поясняется на примере одного из них, 5

Я

33

33

Как только разность фаз между сигналами считывания и записи достигает порогового значения, как правило равного 2 радиан, с контрольного выхода синхронизатора 2 в блок 3 управления стаффингсм поступает сиг..ал, после чего с управляющего выхода блока 3 через передающий коммутатор 5 по высокоскоростному тракту в закодированном виде передается информация о номере синхронизатор", B котором будет осуществлс: а ьставка ба,;iacTIIOI.O такTOIIOIO интервала. В момен; В130.là балласчч1ого такl 013010 и11тервала, опреде,?ясмого структурой объединенного цикла пер дачи, на управляющий вход синх1301111зат013а 2 из Oлonn 3 IIOCT t rt ICT CHI HB i за!113ет?1, 110д Jc?tc Вием ко! opo ° О Б сииxpoIIH заторе будет пропущен одп:1т,акт считывания (осуществлен поло:;

В BTOT ?t e ironic?t t C доно:tit;iTB;Hinor o Baixoда блока 3 на вход генератора поступает сигнал, по которому с выхода генератора 1 на дополнительный вход с.tn. ронизатора 2, в котором осущсствляется вставка балластного тактового интервала, передается сигнал Коптрольной информации «Единица» («Ноль») .

Таким образом, cn

2 поступает на передающий коммутатор 5, откуда передается на приемную сторону.

В следующий момент, когда создадутся условия вставки балластного интервала в другом синхронизаторе, происходит процесс, описанный выше, с той лишь разницей, что на позиции балластного тактового интервала пер дается «Ноль» («Единица»).

Генератор контрольной информации 1 работаег таким образом, что при поступлении на его вход управляющих импульсов от блока управления стаффингом 3 на его вь;.лде ооразуется импульсная последовательность ви;а 10101010... Информация о балластных тактовых интервалах, передаваемая на приемную сторону с выхода приемного коммутатора 7, поступает в блок 9 управления стаффингом.

После декодирования сигнала о наличии балластного тактового интервала в каком-либо из объединяемых цифровых потоков на управляющий вход соответству?ощего десинхронизатора 8 подается сигнал, по которому запись символа контрольной информации, передаваемого на позиции балластного тактового интервала, в устройство памяти десинхронизатора запрещается. Одновременно с дополнительного выхода блока 9 управления стаффингом на один из входов приемника б контрольной информации передается сигнал. по которому символ контрольной информации с дополнительного выхода десинхронизатора

8 поступит на второй вход приемника контрольной информации б и будет принят входным блоком 11 сравнения.

Таким образом, при исправной работе передающей и приемной частей предложенного

563734 устройства на второй вход приемника контрольчой информации 6 с дополнительных выходов десинхронизаторов 8 будет поступать контрольная импульсная последовательность вида 10101010... Блок 11 осуществляет сравнение двух соседних символов; в случае приема подряд двух одинаковых символов с выхода входного блока 11 на вход накопителя 12 поступает импульс. Накопитель 12 обеспечивает защиту от сбоев символов контрольной информации, возникающих в процессе передачи по линейному тракту, и его порог срабатывания выбирается в зависимости от величины вероятности ошпоки в линейном тракте. В случае превышения порога срабатывания накопителя 12 (при неисправной работе передавшей или приемной стороны) на его выходе появляется импульс, фиксируемый счетчиком 13, Для правильного распределения цифровых 20 потоков по десинхронизаторам 8 и декодирования информации о стаффинге в устройстве имеются блоки цикловой синхронизации 10 и

4 соответственно приемной и передающей сторон. 2д

Передача контрольной информации на позициях балластных тактовых интервалов, возникающих при объединении цифровых потоков с положительным стаффингом, позволяет получить устройство для контроля многоканаль- 30 ной системы связи с временным разделением каналов без применения специального контрольного канала.

Таким образом, предложенное устройство имеет высокую точность контроля. 35

Формула изобретения

1. Устройство для контроля многоканальной системы связи с временным разделением ка- 40 налов, содержащее на передающей стороне генератор контрольной информации, синхронизаторы, контрольчые выходы которых подключены к блоку управления стаффингом, соответствующие выходы которого соединены с управляющими входoìH синхронизаторов и входом блока цикловой синхронизации, выход которого, а также информационные выходы синхронизаторов и управляющий выход блока управления стаффингом подключены к соответствуюгц м входам передающего коммутатора, а на приемной стороне — приемнии контрольной информации, приемный коммута. тор, выходы которого подключены к соответствующим входам десинхронизаторов, блока управ", ñHHÿ стаффингом и блока цикловой синхронизации, выходы которого соединены с синхронизирующими входамц десинхронизаторов и блока управления стаффингом, выход которого соединен с управляющими входами десинхронизаторов, о т л и ч а ю щ е е с я тем, что, с целью повышения точности контроля, на передаюшей стороне дополнительный выход блока управления стаффингом подключен к входу генератора контрольной информации, выход которого подключен к дополнительным входам синхронизаторов, а на приемной стороне дополнительный выход блока управления стаффингом подключен к одному из входов приемника контрольной информации, к другому входу которого подключены дополнительные выходы дссинхронизаторов.

2. Устройство по п. 1, отличающееся, Гм, что п11иемнп1 контрольной информации выполнен в виде последовательно соединенных входчсго блока сравнения, накопителя и счетчика.

Источники информации, принятые во внимание прп экспертизе

1. Патент CILIA ¹ 3461245. кл. 179-15, 1969.

563734

Вь код

1 — 1

Составитель Г. Челей

Редактор Е. Дайч

Текред И. Карандашова

Корректор A. Степанова

Заказ 1677/3 Изд. ¹ 578 Тираж 818 Г1 одни свое

ЦНИИПИ Государственного комитета Совета Л1ивистров СССР оо делам изобретений и открытий

1!3035, Москва, уК-3;>, Раушская наб., д. 4/5

Типография, вр. Сапунова, 2

I t!

1

j3