Устройство для синхронизации равнодоступных многоканальных систем связи

Иллюстрации

Показать всеРеферат

; (О П И С А Н И Е (11) 563736

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сс. ов Советских

Содиалистнческнх

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 22.04.75 (21) 2127075 09 с присоединением заявки № (51) М Кл Н 04L 7/06

Н 04J 3/06

Совета Министров СССР по дедал изобретений н открытий (53) УДК 621.394 662 2 (088.8) Опубликовано 30.06.77. Бюллетень № 24

Дата опубликования описания 23.07.77 (72) Авторы изобретения

Б. П. Новиков, С. А. Ганкевич, Н. П. Жаровин, В. Г, Солоненко и А. Н. Баранов

Минский радиотехнический институт (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ

РАВНОДОСТУПНЫХ МНОГОКАНАЛЬНЫХ СИСТЕМ СВЯЗИ

ГосУдаРственный комитет (23) Г1риоритет

Изобретение относится к радиосвязи и может использоваться в многоканальных синхронно-адресных системах связи с временным разделением каналов, в которых обмен информацией между неско IbKHMH приемо-передающими станциями (абонентами) осуществляется на одной частоте в неперекрывающихся интервалах времени.

Известно устройство для синхронизации равнодоступных многоканальных систем связи, содержащее последовательно соединенные фильтр и узел канальной синхронизации (1).

Однако известное устройство требует большого объема синхронизирующей информации.

Цель изобретения — сокращение объема синхронизирующей информации.

Для этого в устройство для синхронизации равнодоступных многоканальных систем связи, содержащее последовательно соединенные фильтр и узел канальной синхронизации, введены узел тактовой синхронизации, узел фазирования и блок определения последнего бита информации, при этом один вход фильтра соединен с входом узла тактовой синхронизации, другие входы которого подключены к соответствующим выходам узла канальной синхронизации, а выходы — соответственно к другим входам фильтра и входам блока определения последнего бита информации и узла канальной синхронизации, дополнительные вход и выход которого соединены с узлом фазирования.

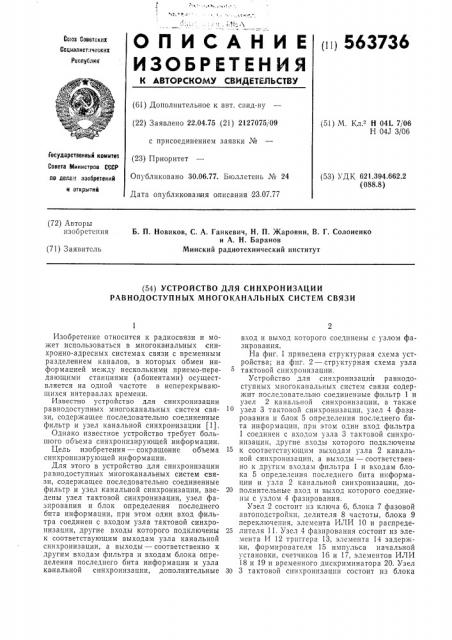

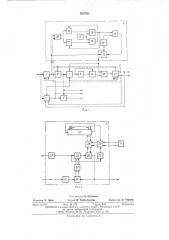

На фиг. 1 приведена структурная схема устройства; на фнг. 2 — структурная схема узла тактовой синхронизации.

Устройство для синхронизации равнодоступных многоканальных систем связи содержит последовательно соединенные фильтр 1 и узел 2 канальной синхронизации, а также узел 3 тактовой синхронизации, узел 4 фазирования и блок 5 определения последнего бита информации, при этом один вход фильтра

1 соединен с входом узла 3 тактовой синхронизации, другие входы которого подключены

15 к соответствующим выходам узла 2 канальной синхронизации, а выходы — соответственно к другим входам фильтра 1 и входам блока 5 определения последнего бита информации и узла 2 канальной синхронизации, до20 полнительные вход и выход которого соединены с узлом 4 фазпрования.

Узел 2 состоит из ключа 6, блока 7 фазовой автоподстройки, делителя 8 частоты, блока 9 переключения, элемента ИЛИ 10 и распреде25 лителя 11. Узел 4 фазирования состоит из элемента И 12 триггера 13, элемента 14 задержки, формирователя 15 импульса начальной установки, счетчиков 16 и 17, элементов ИЛИ

18 и 19 и временного дискриминатора 20. Узел

30 3 тактовой сггн: ронизацпи состоит из блока

563736

21 выделения сигналов синхронизации, временного дискриминатора 22, реверсивного счетчика 23, генератора 24, управителя 25, управляемого делителя 26, кольцевого регистра 27, блока 28 переписи кода, блока 29 формирования импульсов перезаписи и продвижения и делителя 30.

Устройство работает следующим образом.

Входной сигнал поступает на вход узла 3 тактовой синхронизации и на вход фильтра

1. Импульсы синхронизации с выхода фильтра 1 подаются через открытый ключ 6 на блок 7 фазовой автоподстройки, где происходит слежение за фазой принятого сигнала синхронизации.

Состояние блока 9 переключения зависит от режима работы абонента.

Если абонент работает только на прием, то делитель 8 частоты отключен блоком 9 переключения и синхронизация распределителя

11 осуществляется сигналом с выхода блока

7 фазовой автоподстройки.

При работе абонента на передачу и прием в разных временных каналах распределитель

11 синхронизируется сигналами с выхода блока 7 через делитель 8 частоты, который выполняет в этом случае роль развязки. Этим достигается частичная независимость приема и .передачи сигналов синхронизации.

Синхронизация распределителя 11, выполненного на регистре сдвига с обратной связью, производится по установочной шине с выхода блока переключения 9 через элемент ИЛИ 10, а продвижение — импульсами с выхода генератора 24.

Для ускорения времени фазирования узла

2 канальной синхронизации слу кит узел 4 фазирования.

Импульс синхронизации с выхода фильтра

1 через элемент И 12 подается на установочный вход управляемого делителя блока 7 фазовой автоподстройки непосредственно, а также через элемент ИЛИ 10 на установочный вход распределителя 11. Этот яе импульс поступает на один из входов временного дискриминатора 20, где сравнивается с временным стробом позиции последнего элемента сигнала фазирующей комбинации, дешифрируемой с распределителя 11. Разрешение на занесение кода в распределитель 11 и блок 7 фазовой автоподстройки через элемент И 12 осуществляется триггером 13, один из входов которого подключен к выходу элемента И 12 через элемент 14 задержки, другой — к выходу счетчика 16 через элемент ИЛИ 18. Начальная установка счетчиков 16 и 17, триггера 13 производится выходным сигналом формирователя 15 импульса начальной установки через элементы ИЛИ 18, 19. Перекрестный сброс счетчиков 16, 17 осуществляется через элементы ИЛИ 18, 19.

В момент включения питания импульс начальной установки через элементы ИЛИ 18, 19 сбрасывает показания счетчиков 16, 17 и устанавливает триггер 13 на разрешение за5

ЗО

65 несения кода в распределитель 11 и управляемый делитель блока 7 фазозой автоподстройки через элемент И 12. Первый отклик фильтра 1 через элемент И 12 осуществляет первоначальное фазирование распределителя

11 и управляемого делителя блока 7. Задеряаннь:й импульс с выхода элемента И 12 опрокидывает триггер 13 и блокирует элемент И 12. Затем происходит анализ правильности фазирования распределителя 11 и блока 7. Такой анализ осуществляется с помощью временного дискриминатора 20 и счетчиков 16 и 17 с перекрестным сбросом. Если занесение кода было истинным, временной строб с выхода распределителя 11 совпадает с приходом последующих импульсов сигнала синхронизации. Они сравниваются во временном дискриминаторе 20.

В результате происходит переполнение счетчика 17, подключенного к выходу схемы совпадения временного дискриминатора 20, который сбрасывает показания счетчика 16 при каждом переполнении. Если занесение кода произошло ложным импульсом, то переполняется счетчик 16, подключенный к выходу схемы несовпадения временного дискриминатора 20, который перебрасывает триггер 13 на повторное занесение кода через элемент И

12 в распределитель 11 и управляемый делитель блока фазовой автоподстройки и сорасывает счетчик 17.

Процесс повторяется до тех пор, пока фазирование распределителя 11 и блока 7 фазовой автопо. стройки нс осуществляется истиннь.м импульсом синхронизации с выхода фильтра 1.

Открывание ключа 6 осуществляется стробимпульсом позиции последнего элемента сигнала синхронизации с выхода распределителя 11.

После этого ключ 6 закрывается и остается закрытым на протяжении канального интервала до поступления сигнала фазирующей комбинации в следующем временном канале, что исключает прохождение ложных синхроимпульсов на вход блока 7 фазовой автоподстройки.

Синхронизация по тактам осуществляется узлом 3 тактовой синхронизации, в котором происходит запоминание фазы опорного сигнала управляемого делителя 26 в конце каждого временного канала и восстановление ее в начале этого же канала через цикл работы.

Пусть за время приема сигнала «Вызов», который предшествует передаче информационного сигнала в том же временном канале и принимается другим устройством, не требуюьцим знания фазы тактовой частоты, в соответствующем временном канале устраняется рассогласование между опорным и входным сигналами. При этом между эталонным сигналом на выходе делителя 30 и опорным на выходе управляемого делителя 26 устанавливается определенный фазовый сдвиг, Этому фазовому сдвигу соответствует определенный

563736 код управляемого делителя 26 в моменты появления импульсов на выходе делителя 30.

Этот код в конце канального интервала заносится в кольцевой регистр 27 импульсом записи кода, вырабатываемым блоком 29 формирования импульсов перезаписи и продвижения, и привязанным по фазе к эталонному сигналу с выхода делителя 30.

Установка фазы опорного сигнала в начале временного канала производится в обратном порядке импульсом установки кода в управляемом делителе 26. Этот импульс также совпадает по фазе с эталонным сигналом.

Продвижение кода в кольцевом регистре 27 производится пачкой импульсов, следующей в промежутке времени между импульсами записи и импульсом установки кода. Число импульсов в пачке равно числу элементов кода. Выбор длины кольцевого регистра 27 производится с учетом количества временных ка- 20 налов и требуемой точности запоминания фазы.

Таким образом, узел 3 тактовой синхронизации обеспечивает .независимую тактовую синхронизацию по сигналам различных абонентов, работающих в разных временных каналах с различными фазовыми сдвигами тактовой частоты.

Сигналы с выхода узла 3 поступают на фильтр 1, обеспечивая тем самым синхронный 30 прием сигнала фазирующей комбинации.

Импульсы синхронизации с выхода ключа

6 служат для определения первого и последнего бита информации, передаваемой во временном канале. Причем первый бит инфор- 35 мации определяется непосредственно по сигналу с выхода фильтра 1. снимаемого с выхо..а ключа 6, а последний — путем подсчета тактовых импульсов в блоке 5 определения последнего бита информации, в состав которого входит делитель с коэффициентом пересчета, равным количеству символов информационной части сигнала во временном канале.

Подсчет тактовых импульсов в блоке 5 начинается с момента прихода импульса синхронизации с выхода ключа 6 и кончается после переполнения делителя блока 5.

Формула изобретения

Устройство для синхронизации равнодоступных многоканальных систем связи, содержащее последовательно соединенные фильтр ц узел канальной синхронизации, о т л и ч а ющ е е с я тем, что, с целью сокращения объема спнхронизпрующей информации, введены узел тактовой синхронизации, узел фазирования и блок определения последнего бита информации, при этом один вход фильтра соединен с входом узла тактовой синхронизации, другие входы которого подключены к соответствующим выходам узла канальной синхронизации, а выходы — соответственно к другим входам фильтра и входам блока определения последнего бита информации и узла канальной синхронизации, дополнительные вход и выход которого соединены с узлом фазпрования.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 475743, кл. Н 041 7/06, 1973.

Редактор Е. Дайч

Составитель А. Кузнецов

Техред И. Карандашова

Корректор О. Тюрина

Заказ 1677/5 Изд, № 576 Тираж 818 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2