Устройство для ввода данных

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (»> б64взо

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 15 03 76 (21) 2334182/24 с присоединением заявки № (23) Приоритет (43) Опубликовано05.07.77.бюллетень № 25 (45) Дата опубликования описания 17.08.77 (á1) M. Кл. 06 V 3 00

Гааударстааннм» иамнтат

Саавта Миннатрав СССР ао делам нзобрвтвний н атирмтнй (53) УДК 581.327. . 1 1 (088.8) (72) Автор изобретения

И. А. Паатоиов

Таганрогский радиотехнический институт им. B Д. Калмыкова (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВВОДА ДАННЫХ

Изобретение относится к области вычислительной техники и может быть использовано для ввода задач и исходных данный

s UBM.

Известно устройство для ввода данных б

s 11ВМ, содержашее блок ввода, соединенный с блоком памйти, блок преобразования «с дов> выходной преобразователь Pl/, Недостатком данного устройства является его невысокое быстродействие.

Наиболее близким по технической сущности к изобретению является устройство, содержашее входной преобразователь кодов, блок памяти, регистры символов и переменных, выходы которых подключены ко входам шифраторов символов и переменных регистр констант, выход которого соединен со входом выходного преобразователя кодов (2). .Низкое быстродействие такого устрой- 20 ства обусловлено тем, что при вводе задачи, например системы дифференциальных уравнений, записанной на алгооитмическом языке, она без сушественных преобразований передается на устройства ввода в 25 оперативную память ЦВМ, где обрабатыва» ется на специальной программе (трансля.» тор) и преобразуется в процессоре в прог рамму вычисления этой задачи, записанную на машинном языке UBM. Обработка, этой программы для получения решения происходит только после трансляции. Это значительно увеличивает об|цее время реши ния задачи. так как транслирование и ее решение пройсхддят последовательно во вре мени. При этом уменьшается обшее быстродействие устройства, Белью изобретения является повышение быстродействия устройства.

Эта цель достигается,тем, что предложенное устройство содержит блок лексического анализа, входы которого подключе » ны к выходам входного преобразователя кодов и блока памяти, а выходы - ко вхо- дам регистров символом, переменных и констант и входу блока памяти, а также тем, что блок лексического анализа содержит схему сравнения, два триггера, элементы ИЛИ-И и элементы И. При этом выходы схемы сравнения подключены к единичным

564630

3 ,входам триггеров, к первым входам первого и второго элементов ИЛИ-И и первым входам элементов И, вторые входы которых соединены с выходами первого и второго триггеров, нулевые входы которых подключены к выходам одного из элементов И и первого элемента ИЛИ-И, выходы элементов И соединены со входами элементов

ИЛИ-И, другие входы которых подключены к первому входу блока, второй вход кото- о рого соединен со входом схемы сравнения, а выходы элементов ИЛИ-И подключены к выходам блока.

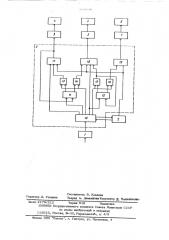

На чертеже представлена блок-схема устройства. 15

Устройство содержит входной преобразователь 1 кодов, блок 2 памяти, регистр

3 символов, шифратор 4 символов, регистр

5 переменных, шифратор 6 переменных, регистр 7 констант, выходной преобразова- 20 тель 8 кодов и блок 9 лексического анализа.

Блок 9 содержит схему 10 сравнения, триггеры 11 и 12, элементы И 13-16 и элементы ИЛИ-И 17-19. 25

Устройство работает следующим образом.

Решаемая задача, записанная на алгоритмическом языке в виде кодов литер, иэ которых составлены слова, через входной преобразователь 1 поступает последователь- ЗО но, литера за литерой, в схему 10 сравиеиия блока 9 лексического анализа, где каждая поступающая литера сравнивается с очередной литерой, записанной в блоке

2 памяти.

В зависимости от сочетания литер в схеме 10 и элементах 13-19 вырабатываются следующие управляющие сигналы.

Если поступающая литера была буквой, а в блоке 2 памяти были также записаны 4о буквы, то поступающая буква записывается в блок 2 памяти и триггер 11 устанавливается в единичное состояние. Если в блоке 2 памяти был записан знак арифметической операции или раэделитель,то по- 4> дается управляющий сигнал на элемент 17

ИЛИ-И и слово из блока 2 памяти записывается в регистр 3 символов, а триггер

11 устанавливается в нулевое состояние.

Если поступающая литера была цифрой, а в блоке 2 памяти была буква, то пода- ется управляющий сигнал на элемент 18

ИЛИ-И и слово из блока 2 памяти записывается в регистр 5 переменных. Одновременпо подается сигнал на единичный вход триггера 12. Если в блоке 2 памяти была цифра, то поступающая цифра записывается в блок 2 памяти. Если в блоке 2 памя ти был знак арифметической операции или оаэделитель, То подается управляющий сиг нал на элемент 17 ИЛИ-И и слово из блока 2 памяти записывается в регистр 3 символов, а триггер 1 1 устанавливается в нулевое состояние, Если поступающая литера была знаком арифметической операции, а в блоке 2 памяти была записана бук, то подается управляющий сигнал на элемент 18 ИЛИ-И и слово из блока 2 памяти записывается в регистр 5 переменных. Одновременно триггер 12 устанавливается в единичное состояние. Если в блоке памяти были записаны цифры, .то в зависимости от состояния триггера 12 подается управляющий сигнал на элементы 18 или 19 ИЛИ-И и слово из блока 2 памяти записывается либо в регистр 5 переменных как индекс переменной, либо в регистр 7 констант.

Если триггер 12 находился в единичном состоянии, то одновременно с записъю слова в регистр 5 переменных он устанавливается в нулевое состояние. Если в блоке 2 памяти был записан,:.разделитель, то подается управляющий сигнал на элемент 17 ИЛИ-И и слово из блока 2 памя ти записывается в регистр 3 символов, а триггер 1 1 устанавливается в нулевое состояние.

Если поступающая литера была разделителем, а в блоке 2 памяти была записана буква, то в зависимости от состояния триггера 11 подается управляющий сигнал на элемент 17 ИЛИ-И или элемент 18

ИЛИ-И и слово из блока 2 памяти записывается либо в регистр 3 символов, либо в регистр переменных. Если в блоке 2 памяти была записана цифра, то в зависимости от состояния триггера 12 подается управляющий сигнал на элемент 18 или элемент 19 и слово из блока 2 памяти записывается либо в регистр 5 переменных, либо в регистр 7 констант. Одновременно триггер 12 устанавливается в нулевое состояние. Если в блоке 2 памяти был записан знак арифметической операции или разделитель, то подается управляющий сигнал на элемент 17 ИЛИ-И и слово из блока 2 памяти записывается в регистр символов, а триггер 1 1 устанавливается в нулевое состояние.

Слово, запиоанное в регистре 3 символов или в регистре 5 переменных, пере кодируется в соответствующем Шифраторе

4 или 6 таким образом, чтобы каждое из них имело одинаковую длину и имело все необходимыесинтаксические и семантические признаки для последующего анализа, Число, записанное в регистре 7 констант, преобразуется в выходном преобразователе

8 в машинную систему счисления.

564630:

Предложенное устройство позволяет. иск ключить иэ процесса трансляции задачи эт .ап лексического анализа, который ящщ ется одним из наиболее трудоемких и для выполнения которого обьсчнсспользуют арифметическо-логический блок ЦВМ. Это позволяет значительно сократить время ре;шения задачи и тем самым повысить ско рость ввода данных.

Формула иэрбретения

1. Устройство для ввода данных, содержашее входной преобразователь кодов, блок памяти, регистры символов и переменных, выходы которых подключены ко входам шифраторов символов и переменных, регистр констант, выход которого соединеь со входом выходного преобразователя ко» дов,отличаюшееся тем,что, с целью повышения быстродействия устройства, оно содержит блок лексического анализа, входы которого подключены к выходам входного преобразователя кодов и блока памяти, а выходы — ко входам регистров символов, переменных и констант и входу блока памяти.

2. Устройство по п, 1, о т л и ч а ющ е е с я тем, что блок лексического анализа содержит схему сравнения, два триггера, элементы ИЛИ-И и элементы И при этом выходы схемы сравнения подключены к единичным входам триггеров, к

% первым входам первого и второго элемен гов ИЛИ-И и первым входам элементов И, вторые входы которых .соединены с выхода10 ми первого и второго триггеров, нулевые входы которых подключены к выходам одного из элементов И и первого элемента

ИЛИ-И; выходы элементов И соепинепы со входами элементов ИЛИ-И, другие входы

15 которых подключены к первому входу блока, второй вход которого соединен со входом схемы сравнения, а выходы элементов

ИЛИ-И подключены к выходам блока.

Источники информации, принятые во внимание при экспертизе:

1, Майоров С. А. Новиков Г. И. Принцип организации цифровых машин . М., Машиностроение," 1974, стр. 411-412.

2. EC-2020, Селекторный канал, тех« ническое описание Е 1 3 0 55,00Й Т03, 1971 r.

Редактор Л. Утехина

Составитель В. Ковалев

Техред А. демьянова Корректор й, Мельниченко

Заказ 2179/212 Тираж 818 Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскаянаб., д. 4/5 о

Филиал ППП Патент", г. Ужгород, ул, Проектная, 4