Устройство для сравнения двоичных чисел

Иллюстрации

Показать всеРеферат

ОП ИСАЙЯМИ

ИЗОБРЕТЕНИЯ! (11) 564632 т.. оюз Советских

Социалистических

Республик

К АВТОРСКОМУ СооИДЕТИДЬСТВУ (61) Дополнительное к авт, свид-ву— (22) Заявлено 01.08.75(21) 2160551/24 (Ь1) М. Кл.

> 06 Р- 7/04 с присоединением заявки № (23) Г1рноритет

Государственный номнтет

Соввта Мнннотроо СССР оо делам нэобрвтеннй н отнрытнй

Р3) УД1 68 t ..325..65 { 088.8) (43) Опубликовано 05 07 774зюллетень №25 (45) Дата опубликования описания 1.7.08.77 (72) Авторы изобретения

М. П. 1 иРЮчеико, А. М. Саркисов, А. Г, Мангасаров и 8. С. Бурминсхий

Специальное проектно-конструкторское бюро средств автоматизм ни добычи нефти, кранспорта и хранения газа (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при технической реализации арифметических устройств для сравнения чисел. 5

Известны устройства для сравнения двух двоичных чисел jlj,(21,содержащие схемы выделения сигнала о неравнозначности в более старшем разряде, если неравнозначность существует одновременно в несколь тО ких разрядах сравниваемых чисел.

Однако известные устройства для сравнения чисел большой разрядности содержат сложные схемы выделения сигналов о неравноэначности в наиболее старшем оазряде 15 эа счет использования не менее одного транзистора на каждый разряд сравниваемых чисел.

Наиболее близким техническим решением к изобретению является устройство для 20 сравнения двоичных чисел, содержащее источник опорных напряжений, выходные шины которого подключены к шинам питания поразрядных ячеек сравнения, состоящих из двух элементов И, входы каждого иэ 25 которых подключены к соответствующим входным шинам устройства, а выходы— к выходным шинам поразрядных ячеек сравнения пороговый элемент и элемент ипи-не з1.

Недостатком этого устройства являет ся сложность схемы поразрядных ячеек сравнения, так как в них используется по одному транзисторному ключу, работаюшему в цепи вьщеления сигнала о неравноз начности в наиболее старшем разряде.

11елью изобретения является упрощение устройства.

Эта цель достигается тем, что предложенное устройство содержит два узла выделения максималтного напряжения, входы которых соединены с соответствующикот выходами поразрядных ячеек сравнения, а выходы — со входами порогового элемента. выходы которого подключены к первой и второй выходным шинам устройства и через элемент ИЛИ-НЕ к третьей выходной шине устройства.

564632

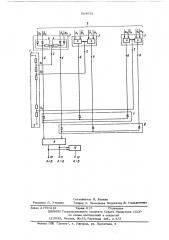

Блок-схема усг ройстьи представлена на ч" рг еже

Устройство содержит источник опорных напряжений lq выходные шины которого

Подключены к шинам питания 2 норазрйд 5 ных ячеек сравнения 3, состоящих из двух элементов И 4, входы каждого из которых подключены к соотьетствуюшим ьходным шинам 5 устройства, а выходы через выходные шины 6 поразрядных к сравне- 10 ния 3 — ко входам соответствующих узлов выделения максимального напряжения 7,8, Выходы последних подключены ко входам порогового элемента 9, выходы которого подключены к выходным шинам lO, ll 15 устройства и через элемент ИЛИ-HE 12 к выходной шине 13 устройства, Устройство работает следующим образом, Если сравниваемые числа А я В между собой равны, то на выходах всех, ячеек сравнения 3 напряжение сигналов равно нулю, а следовательно, на выходах узлов

7, 8 и на выходах порогового элемента 9 напряжение сигналов также равно нулю (ниже установленного доиога чувствительности элемента 9). В результате на оооих выходах порогового элемента 9 формируются сигналы логического нуля. На выходе элемента ИЛИ-НЕ 12 и на шине

13 появляется сигнал логической единицы, что соответствует признаку А = В, Если сравниваемые числа А и Б не равны между собой, то в одной или нескольких ячейках сравнения 3 окажутся открытыми по одному элементу И 4, на выходах которых появляются сигналы, напряжения которых равны соответствующим опорным напряжениям. Эти сигналы поступают по шина м 6 на. входы соответствую- 40 щих узлов 7, 8. Причем по входу узла 7 поступают формируемые эл*ментами И 4 сигналы с признаками поразрядной нераянозначности типа А В, а по входу узла

8 — сигналы с признаками В > А

Выделенные узлами7, 8 сигналы максимального напряжения поступают на соответствующие входы порогового элемента 9.

Если напряжение выходного сигнала узла

7 больше напряжения выходного сигнала

50 узла 8, то пороговый элемент 9 выдает иа вторую выходную шину 1 1 сигнал логической единицы, что соответствует признаку

А>В. Если же на выходе узла 7 напряжение сигнала меньше, чем на выходе узла 8, то пороговый элемент 9 выдает сигнал логической единицы на первую выходную шину 10, что соответствует признаку А В.

Источник опорных напояжений 1 может

60 быть выполнен, например, как делитель напряжения на резисторах, число выходов которого соответствует числу ячеек сравнения 3 устройства. Причем опорное напряжение О источника опорных напряжений 1, подаваемое на ячейку сравнения 3 младших разрядов, наименьшее, а опорное напряжение З,„, подаваемое на ячейку сравнения 3 старших разрядоь, наибольшеф.

Узлы выделения максимального напря-, жения 7, 8 могут быть выполнены, например, на диодах, общие точки соединения которых являются выходами узлов.

Пороговый элемент,9 может представлять собой, например, дифференциальный каскад с релейной выходной характеристи кой и установленным порогом чувствительности, несколько меньшим, чем опорное напряжение Б1 на выходе источника опорных напряжений 1.

Предлагаемое устройство отличается от известных схемной простотой, так как содержит меньшее число элементов, приходящихся на один разряд сравниваемых чисел, Преимуществом устройства является также его высокая надежность, FGK как оно может быть выполнено практически только на диодах„и резисторах, а также высокое быстродействие, достигаемое за счет парад.лельного анализа поразрядных неравнозначностей, Формула изобретения

Устройство для сравнения двоичных чи сел, содержащее источник опорных напряжений, выходные шины которого подключены к шинам питания поразрядных ячеек сравнения, состоящих из двух элементов И, входы каждого из которых подключены к соответствующим входным шинам устуойства, а выходы — к выходным шинам поразрядных ячеек сравнения, пороговый элемент и элемент ИЛИ-НЕ, о т л и ч а ю щ е е с я тем, чтст, .с целью упрощения устройс гва, оно содержит два узла выделения мак-симального напряжения, входы которых сое-, динены. с соответствующими выходами пораЭ рядных ячеек сравнения, а выходы — совхоз дами порогового элемента, выходы которо» го подключены к первой и второй выходным шинам устройства,и через элемент ИЛИ-НЬ к третьей выходной шине устройства.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

N0 322457, 5 06 F 7/00, 14.03,72 r.

2. Авторское свидетельство СССР

N. 341032, Я. 06 Р. 7/02> 05.06.72 r.

3,. Авторское свидетельство СССР

N 289413 g 06 Р 7/02, 08.12.70 г.

564632

Ac@ ф д д=д

Составитель В. Белкин

Техред A. демьянова Корректор И. Мельниченко

Редактор Л. Утехина

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 2179/212 Тираж 815 .Подписное

UHHHHH Государственного комитета Совета Министров СССР по делам изобретений и открытий

123035, Москва, Ж-35, Раушская наб., a. 4/5