Цифровой умножитель частоты

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДГТВЛЬСТЬУ (ii) 566298 (61) Дополнительное к авт. свид-ву (22) Заявлено 04.12,75 (21) 2195618/21 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.07.77.Бюллетень № 27 (45) Дата опубликования описания 11.08,77

2 (51) М. Кл.

Н 03 В 19/12

Гааударатвенний комитет

Совета Министров СССР оо делам изобретений и открытий (53) У ДК 62 1. 37 5, 2 (088,8) (72) Авторы изобретения

B. B. Смеляков, В, И. Бармин, H. М. Булгаков и Л. Е, Шахновский

Харьковский институт радиоэлектроники (71) Заявитель (54) ЦИФРОВОЙ УМНОЖИТЕЛЬ ЧАСТОТЫ

Изобретение относится к импульсной технике.

Известен цифровой умножитель частоты, содержаший генератор импульсов опорной частоты, устройство, формируюшее импуль сы 0 < в момент перехода напряжения умножаемой частоты через нулевые значения, блок управления, электронные ключи, муль тивибратор, делитель частоты с постоянным коэффициентом деления, равным коэффициен- Я ту умножения К,управляемый делитель частоты с переменным коэффициентом деления, схемы переноса и регистры памяти (1).

Недостатком данного умножителя являе ся его сложность. 15

Наиболее близким по технической сушности к предлагаемому является умножитель, содержаший генератор импульсов, выход которого соединен через первый механический ключ с первым входом блока управ-20 ления и непосредственно с первыми входа-. ми двух электронных ключей, вторые входы которых соединены с первым и вторым выходом блока управления, выходы одного из которых соединены со вторым входом блока 35 управления, третий выход которого через механический ключ соединен со своим третьим входом и с первыми входами регистра памяти и управляемого делителя частоты, причем второй вход регистра памяти соединен с выходом первого электронного ключа, а выход регистра памяти соединен через блок переноса со вторым входом управляемого делителя частоты, выход которого подключен к четвертому входу блока управления, à era четвертый выход соединен со входом блока коррекции (2).

Однако такой умножитель не обладает достаточным быстродействием.

11елью изобретения является повышение быстродействия.

Это достигается тем, что в умножитель, содержаший генератор импульсов, выход которого соединен через первый ключ с первым входом блока управления и непосредст венно с первыми входами второго и третьего ключей, вторые входы которых соединены с первым и вторым выходом блока управления, второй вход которого соединен с выходом.второго ключа и с первым входом ре566298 гистра памяти, а третий выход — через четвертый ключ соединен со своим третьим входом, со вторым входом регистра памяти и с первым входом управляемого делителя частоты, а выход регистра памяти соединен

5 через блок переноса со вторым входом управляемого делителя частоты, выход которого подключен к четвертому входу блока управле»ия, четвертый выход которого соединен со входом блока коррекции, введены IO два логических элемента ИЛИ, входы первого из которых соединены с выходами блока коррекции.и третьего ключа, а его выход подключен к третьему входу управляемого делителя частоты, входьi второго логическо-,5

ro элемента ИЛИ соединены с выходом управляемого делителя частоты и пятым выходом блока управления, а его выход подключен ко второму входу блока переноса.

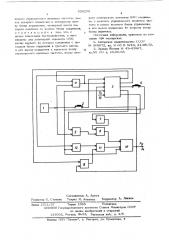

На чертеже приведена структурная элек- 20 тряческая схема предлагаемого умножителя.

Умиожитель содержит генератор 1 импулЬсов опорной частоты, механический ключ цуск" 2, блок 3 управления, электронные ключи 4 и 5, механический ипоч сброс" 6, 2> блок 7 коррекции, логические элементы

ИЛИ- 8 и 9, управляемый делитель 10 частоты, блок 11 переноса, регистр 12 памяти.

Входной сигнал подается на вход 13. ВыхоДной сигнал снимается с выхода 14. Источники сигнала и напряжения на схеме не показаны.

Работа цифрового умножителя частоты осуществляется следуюшим образом.

При нажатия ключа сброс" 6 триггеры (не показаны) блока 3 управления, делителя 10 частоты, регистра 12 памяти устанавливаются в нулевое состояние сигналом с блока управления 3. Электронные ключи

4 и 5 закрыты. Бдоку управления 3 задают 40 код числа И, соответствующий заданному периоду сигнала умножаемой частоты, и требуемый коэффициент умножения К.

Нажимают ключ «пуск" 2. Блок управления 3 выдает сигнал 9, который откры- 4 вает электронный ключ 4, В этот момент начинается подготовительный период, в течение которого импульсы генератора 1 импульсов опорной частоты 1 поступают через открытый электронный ключ 4 в блок Зуправления и регистр 12 памяти, представляющий собой суммирующий счетчик.

После прихода в блок управления 3f Q 3 импульсов частоты о в нем запоминается остаток а11 * 1(- а.П, блок 3 управления зафкрывает электронный ключ 4 и затем выдает сигнал Ч, который проходит через элемент ИЛИ 8, поступает на блок 11»ереноса и переписывает код числа, занеД 111 . j-- —

K где

Таким образом, погрешность смешения

1Ь

g4 =т а и

1 иД Yp я где 1 — номер импульса на выходе умножител я час тоты.

Лля того чтобы погрешность::мешения не превысила Тц, производится коррекция.

В этом сдучае блок 3 управления выдает сигнал V блоку 7, который вырабатывает импульс, через элемент ИЛИ 9 поступаюший на вход делителя 10 частоты и уменьшающий на единицу его содержимое, что эквивалентно уменьшению I. Q)»a единицу.

Формула изобретения

Цифровой умножитель частоты, содержащий генератор импульсов, выход которого соединен через первый ключ с первым входом блока управления и непосредственно с первыми входами второго и третьего ключей, вторые входы которых соединены с первым и вторым выходом блока управления, второй вход которого соединен с выходом второго ключа и первым входом регистра памяти, а третий выход через четвертый ключ соединен со своим третьим входом, со вторым входом регистра памяти и с первым входом управляемого делителя частоты, а выход регистра памяти соединен через блок переноса со вторым се»ный »а регистр 12 па:.яти (в регистр ъ.

12 записан код числа Q) ), в делитель

10 частоты, представляюший собой вычитаюший счетчик.

Через некоторое время блок 3 управления выдает сигнал V>, открывающий электронный ключ 5. В этот момент оканчивается подготовительный период.

Через открытый электронный ключ 5 и элемент ИЛИ 9 импульсы опорной частоты fz генератора 1 импульсов поступают на вход делителя 10 частоты, коэффициент деления которого равен (с ) .

Импульсы умножен»ой частоты на выходе делителя 10 следуют с периодо..: T„=T (gf

Каждый из этих импульсов через элемент 8, блок 11 переноса переписывает код числа (, j с регистра 1 2 в делител ь 1 0 час тоты и в блок 3 управления.

Йля умножения без погрешности период следования импульсов умноженной частоты должен быть равным т, „„= т,(r. l- (+)), 566298

3 4

Составитель A. Артюх

Редактор O. Степина Техред И. Асталощ Корректор А. бавкида

Заказ 2511/37 Тираж 1065 Подписное

III-1ИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 входом управляемого делителя частоты, выход которого подключен к четвертому входу блока управления, четвертый выход которого соединен со входом блока коррекции, отличаюыийс я тем, что,с целью повышения быстродействия, в него введены два логических элемента ИЛИ, входы первого из которых соединены с выходами блока коррекции и третьего ключа, а его выход подключен к третьему входу управляемого делителя частоты, входы второго логического элемента ИЛИ соединены с выходом улравляемого делителя частоты и пятым выходом блока управления, а его выход подключен ко второму входу блока переноса.

11сточпики информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

% 369672, кл. Н 03 В 9/10, 21.08.72.

2. Заявка Японии Ие 43-43867, кл.98 /5/ д, 26.06.68.