Временной дискриминатор

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (и, 566ззв изов итиния

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (51) М. Кл, (22) Заявлено 08.08,75(21) 2160978/21

Н 03 К 5/18 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.07.77,Бюллетень № 27 (45) Дата опубликования опнсания107.09,77

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий (53) УДК 621.373.3 (088.8) (72) Автор . изобретения

Г. K. Вязмитин (71) Заявитель (54) ВРЕМЕННОЙ ДИСКРИМИНАТОР

Изобретение относится к импулъсной технике.

Известен; временной: дискриминатор, содержащий триггеры, разделитель величины угла рассогласования в длительность (1), Такой дискриминатор нв обладает достаточной разрешающей способностью..

Известен также временной дискриминатор, содержащий два триггера,,один вход каждого из которых соединен с источником опор- 6 ного напряжения, а второй вход каждого из которых соединен с источником сигнала, ждущий генератор временного интервала, . состоящий из четырех последовательно соединенных линий задержки, вход первой из ко- И торых соединен с выходом одного триггера, а вход четвертой линии задержки соединен с выходом другого триггера, причем выход первой из упомянутых линий задержки соединен с одним входом логического элемента 20

И, второй вход которого соединен с выходом третьей линии задержки соединен с третьим входом второго из упомянутых триггеров, при этом выход логического элемента И со-, единен со входом интегратора (21, Такой 25 дискриминатор не обеспечивает надлежащей разрешающей способности.

Цель изобретения - повышение разрешающей способности. Это достигается тем, что во временной дискриминатор, содержащий два триггера, один вход каждого из которых соединен с источником опорного напряжения, а второй вход каждого нз которых соединен с источником сигнала, ждуший генератор интервала, состоящий из четырех последовательно соединенных линий задержки, вход первой из которых соединен с выходом одного триггера, а вход четвертой линии задержки соединен с выходом другого триггера, причем выход первый из упомянутых линий задержки соединен с однимвходом логического элемента И, второй вход которого соединен с выходом третьей ли нии задержки, а выход второй линии задержки соединен с третьим входом второго из упомянутых триггеров, при этом выход логического элемента И соединен со входом интегратора, введены две дополнительные управляемые линии задержки, вкюпоченные; последовательно с упомянутыми основными

566338 линиями задержки, и дополнительный логический элемент И, входы которого соединены с выходом четвертой и выходом второй дополнительной линии, задержки, второй выход которой соединен со входом управления первой линии задержки, причем вход управления первой дополнительной линии задержки1 соединен с первыми входами триггеров, выход первой дополнительной линии задерж ки подключен к третьему входу первого три р гера, а выход дополнительного логического элемента И соединен со вторым входом интегратора.

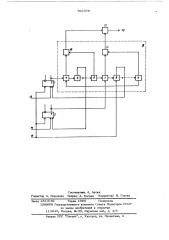

Структурная электрическая схема дискриминатора приведена на чертеже.

Дискриминатор содержит триггеры 1, 2, ждущий генератор 3 временного интервала, состоящий иэ последовательно соединенных пиний 4-9 задержки, логических элементов

И 10, 11, интегратора 12. Нв входы 13 ! и 14 поданы входные сигналы, на вход 15 опорный сигнал, выходной сигнал снимается с выхода 16.

Временной дискриминатор работает следующим образом.

Входные сигналы ИВх(и Иихф ° посту на триггеры 1, 2, устанавливают их в 1

От напряжений с выходов триггеров 1 и 2 запускаются линии 4 и 7 задержки, формирующие импульсы И,<, И„, длительность которых определяется параметрами этих линий задержки. От задних фронтов импульсов И, И, запускаются пинии задержки

5, 6. Кроме того, каждая следующая линия задержки запускается от заднего фронта импульса, сформированного предыдущей ячейкой задержки, в результате чего генератор 3 входит в режим генерации, периодически воспроизводя зафиксированные на ее входах временные интервалы.

Срыв генерапии осуществляется сигналом Ир„. Из этих временных интервалов посредством логических элементов И 10 и

11 формируются импульсы, длительности ко-, торых равны зафиксированным на входе устройства временным интервалам:

c„„- „=pi à (,-а.Д-РГ, -А,- . / где P - количество периодов, генериру50 емых ждущим генератором временного интервала;

Т, — длительность импульса, формируемого i — ой ячейкой задержки.

Импульсы нв элементе 10 формируются в том случае, когда сигнал И приходит

Вх1 раньше сигнала И 2 импульсы на элементе

Зх2

11 формируются в том случае, когда сиг» нвл И „. поступает позже сигналя Иихф °

Импульсы с элементов 10, 11 поступают на входы интегратора 12, выдающего постоянное напряжение положительной полярности при наличии на его входе сигнала с выхода элемента 10 отрипатепьной полярности и при наличии на его входе сиг:нала с выхода элемента 11.

Величина этого напряжения пропорциональна длительности временного интервала между входными сигналами И „и И „, формула изобретения

Временной дискриминатор, содержащий два триггера, один вход каждого из которых соединен с источником опорйого напряжения,!а второй вход каждого из которых соединен с источником сигнала, ждущий генератор временного интервала, состоящий иэ четырех последовательно соединенных линий задержки, вход первой из которых сое- динен с выходом одного триггера, .а вход четвертой линии задержки соединен с выходом другого триггера причем выход первой иэупомянутых линий задержки соединен с одним входом логического элемента И, вто- рой вход которого соединен с выходом третьей линии задержки, а выход второй линии задержки соединен с третьим входом второго из упомя/ нутых триггеров, при этом выход логического элемента И соединен со входом интет ратора, отличающийся тем, что, с целью повышения разрешающей способности, в него введены две дополнительные управляемые линии задержки, включенные последовательно с упомянутыми основными линиями задержки, и доцопнительный логический элемент И, входы которого соединены с выходом четвертой и выходом второй дополнительной пинии задержки, второй выход которой соединен со входом управления первой линии задержки, причем вход управления первой дополнительной ли« нии задержки соединен с первыми входами триггеров, выход первой дополнительной линии задержки подключен к третьему входу первого триггера, а выход дополнительного логического элемента И соединен со вторым входом интегратора.

Источники информации, принятые во внимание при экспертизе:

1. Патен США No 3475062,, кл. 307-232, 15.09.69., 2. Авторское свидетельство М 297002,: кл, 6 01 R 25/00, 08,05.69.

566338

Составитель А, Артюх

Редактор А. Морозова Техред I А. Богдан Корректор И. Гоксич

Заказ 2513/39 Тираж 1065 Подлисное

ЦИИИЛИ Государственного комитете Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент», r. Ужгород, ул. Проектная, 4