Устройство для декодирования импульсной последовательности

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, свид-ву (22) Заявлено 22,01.76 (21) 2319128/09 (ll) д66 3 18 (я) м. к . с присоединением заявки №

Н 03 К 13/22

Государственным комитет

Совете Министров СССР по делам изооретений н открытий (23) Приоритет (43) Опубликовано25.07.77.Бюллетень № 27 (53) УДК 621 376 2 (088,8) (4б) Дата опубликования опнсания07.09,77

Е, Н, Максаков, A. С, Ибрагимов и B. Д. Лосев (72) Авторы изобретения

i (71) Заявитель . Ленинградский ордена Ленина электротехнический институт имени В, И. Ульянова (Ленина) (54) УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ИМПУЛЬСНОЙ

ПОСЛЕДОВАТЕЛЬНОСТИ

Изобретение относится к импульсной . технике и может использоваться при обработке импульсных сигналов.

Известно устройство для декодирования импульсной последовательности, содержаmee генератор импульсов, выход которого подключен к управляющему входу элемента задержки, и ц . элементов совпадения по числу интервалов в импульсной последовательности 11)

l0

Однако известное устройство имеет недостаточно высокую помехоустойчивость.

Бель изобретения - повышение помехоустойчивости, Это достигается тем, что в устройство 1к для декодирования импульсной последовательности, содержащее генератор импульсов, выход которого подключен к управляющему входу элемента задержки, и тт " элементов совпадения по числу интервалов в им- gp пульсной последовательности, введены "тт дешифраторов адресов ступеней декодирования по числу интервалов в импульсной последовательности и блок адресации ступеней декодирования, при этом выходы блояа ад- 25 ресации ступеней декодирования подключены к адресным входам элемента задержки, к выходам которого подключены входы". соответствтющих дешифраторов адресов ступеней декодирования, выходы каждого из которых подключены к первым входам соответствующих и элементов совпадения, вторые входы т " элементов совпадения объединены и подключены к сигнальному входу элемента задержки, а выходы д элементов совпадения подклю чены к соответствующим входам блока адресации ступеней декодирования.

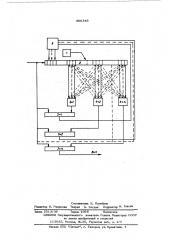

На чертеже изображена структурная электрическая схема предложенного устройGTB8, Устройство содержит генератор импульсов 1, выход которого подключен к управляющему входу элемента задержки 2, и "ут элементов совпадения 3=1-3= r1 по числу интервалов в импульсной последовательности, тт " дешифраторов 4=1-4= rt адресов ступеней декодирования по числу интервалов импульсной последовательности, и блок адресации 5 ступенейдекодирования, при

566348 этом выходы блока адресации 5подключены к адресным входам элемента задержки 2, к выходам которого подключены входы ооой» ветствук>щих дешифраторов 4 = 1-4= и, выходы каждого из которых подключены к первым входам соответствующих элементов совпадения 3 1-3 rt, вторые входы которых объединены к подключены к сигнальн му входу элемента задержки 2, а выходы

1 элементов совпадения 3=1-3 tl подключе- 0 ны к соответствующим входам блока адреса-, ции 5 ступеней декодирования.

Устройство работает следующим образом.

Первому импульсу, поступшощему на вход элемента задержки 2, приписывается адрес-, ный код А <> .соответствующий первому интервалу импульсной последовательности. С приходом второго импульса первый импульс со своим адресным кодом поступает на вход дешифратора 4 1 адресов ступеней декоди- >й рования. Срабатывает элемент совпадения

3 1, фиксируя момент декодирования первой ступени в блок адресации ступеней декодирования 5, и второму импульсу приписывается адресный код А,который опознается следующим дешифратором 4 2. С поступлением на вход элемента задержки 2 последнего импульса последовательности и пред,последнего импульса с адресным кодом

А„Hs вход дешифратора 4 и адресов.сту. ЭО пеней декодирования срабатывает дешифратор 4= и и выходной элемент совпадения

3=. .

Предложенное устройство по сравнению с известным позволяет повысить помехоус-. 5, тойчивость передачи информации за счет более эффективного декодирующего алгорит4 ма. Повышенная эффективность достигается путем адресации каждого входного импульса, что повышает разрешающую способность устройства, Формула изобретения

Устройство для декодирования импульсной последовательности, содержащее генератор импульсов, выход которого подключен к управляющему входу элемента задержки и у элементов совпадения по числу интерва-, лов в импульсной последовательности, о т ! л и ч а ю щ е е с я тем„что, с целью повышения помехоустойчивости, введены n " дешифраторов адресов ступеней декодирования по числу интервалов в импульсной последовательности и блок адресации ступеней

I декодирования, при этом выходы блока «адресации ступеней декодирования подключены к адресным входам элемента за- . держки, к выходам которого подключецы входы .ц соответствующих дешифраторов адресов ступеней декодирования, выходы каж- дого из которых подключены к первым входам соответствующих ".tf элементо.з coBB&» дения вторые входы и. элементов совпа-. дения объединены и подключены к сигнальному входу элемента задержки, а выходы

Н элементов совпадении подключены к соответствующим входам блока адресации ступеней декодирования.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

Мо 515277,кл.. Н 03 К 13/00, 1974.

566348

Составитель Е. Погиблов

Редактор Н, Разумова Текред А. Богдан Корректор H Гокси"

Заказ 2513/39 Тираж 1О65 Подписное

ЦНИИГ1И Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб„д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4