Устройство синхронизации дискретной фазовой автоподстройки

Иллюстрации

Показать всеРеферат

О Il

Союз Советских

Социалистииеских

Республик (1() 566378 (6!) Дополнительное к авт. свнд-ву— (22) Заявлено11. 12.75 (21)2302431/09 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано25.07.77, Бюллетень № 27 (5I) М. Кл

Н 04 1 7/02

Государственный комитет

Совете Министров СССР оо делам изобретений и открытий (53) УДК621.394.

;66 2 { 088. 8) (45) Дата опубликования описания 31.08.77 (72) Авторы изобретения

В, Д, Кутернега, А. В. Папина и А, A. Шахин (71) Заявитель (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ДИСКРЕТНОЙ

ФАЗОВОЙ АВТОПОДСТРОЙКИ

Изобретение относится к электронной технике и может использоваться для синхронизации дискретной фазовой автоподстройки.

Известно устройство синхронизации дискретной фазовой автоподстройки, содержащее триггер памяти и последовательно соединенные регенератор входного сигнала, инвертор первый элемент И и- элемент ИЛИ,. причем к второму входу первого элемента И подключен один из выходов триггера управле- щ ния, между другим выходом и первым входом которого включены последовательно соединенные второй элемент И, второй вход которого соединен с входом регенератора входного сигнала, и формирователь импуль- 10 сов сброса f 1 j .

Однако в известном устройстве время вхождения в синхронизм местного генератора нестабильно и имеет большую величину. 20

11ель изобретения — сокращение времени вхождения в синхронизм.

Для этого в устройство синхронизации дискретной фазовой автоподстройки, содержащее триггер памяти и последователь- 5 но соединенные регенератор входного сигнала, инвертор, первый элемент И и::,элемент ИЛИ, причем к второму входу первого элемента И подключен один:из выходов триггера управления, между другим выходом и первым входом которого включены последовательно соединенные второй элемент И, второй вход которого соединен с входом регенератора входного сигнала, и формирователь импульсов сброса, введены дополнительные формирователь импульсов, инвертор, первый, второй и третий элементы И, при этом вход регенератора входного сигнала через последовательно соединенные первый дополнительный элемент И и дополнительный формирователь импульсов соединен с первым входом триггера памяти, выход . которого подключен к второму входу первого дополнительного элемента И, кроме того, выход дополнительного формирователя импульсов через дополнительный инвертор подключен к первым входам второго и третьего дополнительных элементов И, выходы которых подключены соответственно к второму входу триггера управления и второму

5(36378 входу элемента ИЛИ, причем на вторые входы триггера памяти второго и третьего дополнительных элементов И поданы соответственно сигналы коррекция, "исключение импульсов" и "добавление импульсов".

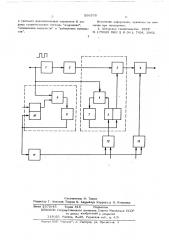

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство содержит последовательно соединенные регенератор 1 входного сигна° ла, инвертор 2, первый элемент И 3 и элемент ИЛИ 4; ко второму входу первого элемента И 3 подключен один из выходов триггера управления 5, между другим выходом и первым входом которого включены последо- д5 вательно соединенные второй элемент И 8, второй вход которого соединен с входом регенератора 1 входного сигнала и формирова1 тель импульсов сброса 7. Вход регенератора 1 входного сигнала через последователь-:20 но соединенные первый дополнительный элемент И 8 и дополнительный формирователь импульсов 9 соединен с первым входом триггера памяти 10, выход которого подключен ко второму входу первого, дополнительного 5 элемента И 8. Выход дополнительного формирователя имлульсов 9 через дополнителт ный инвертор 11 подключен к первым входам второго 12 и третьего 13 дополнительных элементов И, выходы которых под. лючены 30 соответственно ко второму входу триггера управления 5 и втброму входу элемента ИЛИ

4, причем на вторые входы триггера памяти

10, второго 12, и третьего 13 дополнительных элементов И поданы соответственно 55 сигналы "коррекция, "исключение импульсов" и добавление импульсов

Устройство работает следующим образом.

Если импульс коррекции отсутствует, то последовательность импульсов поступает на 50 вход устройства и через регенератор 1 узкого импульса, привязанного к переднему фронту входных импульсов, инвертор 2, первый элемент И 3 и элемент ИЛИ 4 поступает на выход устройства. б

Если импульс коррекции воздействует на вход триггера памяти 10 и поступает сигнал исключение импульса", то импульс коррекции устанавливает посредством переброса триггера памяти 10 разрешение для вход-5О ных импульсов, через первый дойолнительный элемент И 8, которые затем преобразуются в узкие импульсы, привязанные к заднему фронту входных импульсоь с помощью формирователя импульсов 9. 55

Установка триггера памяти 10 в исходное состояние происходит очередным входом импульса. Импульс с выхода формирователя или!ульсов 9 через инвертор Il поступеет также на входы алел.снтов И 12, 13. Импульс через открытый элемент И 12 устанавливает триггер управления 5 в состояние, при котором элемент И 8, открыт а элемент И 3 закрыт. Такое состояние продлится до конца очередного входного импульса и тем самым этот импульс будет

"выбит" иэ серии. Формирователь импульсов

7 выдает узкий импульс, привязанный к концу входного импульса, и триггер управления 5 устанавливается в исходное состояние, при котором входные импульсы проходя через элемент И 3.

Если импульс коррекции воздействует на вход триггера памяти 10 и поступает управляющий сигнал "добавление импульса," то работа триггера памяти 10, элемента

И 8, формирователя импульсов 9, инвертора

11 аналогична описанной выше. Импульс с инвертора 11 через открытый элемент

И 13 и через элемент ИЛИ 4 поступает на выход устройства, и между двумя выходными импульсами добавляется еще один импульс, сформированный по заднему фронту первого входного импульса.

Предложенное устройство позволит сократить время вхождения в сикхрониэм.

Формула изобретения

Устройство синхронизации дискретной фазовой, автоподостройки, содержащее три гер памяти и последовательно соединенные регенератор входного сигнала, ивентор, первый элемент И и элемент ИЛИ, причем к второмувходу первого элемента И подключен один из выходов триггера управления, между другим выходом и. первым входом которого включены последовательно соединенные второй элемент И, второй вход которого соеднен с входом регенератора входного сигнала и формирователь импульсов сброса, о т л ич а ю щ е е с я тем, что, с целью сокращения времени вхождения в синхрониэм, введены дополнительные формирователь импульсов, инвертор, первый, второй и третий элементы И, при этом вход регенератора входного сигнала через последовательно соединенные первый дополнительный элемент

И и дополнительный формирователь импульсов соединен с первым . входом триггера памяти, выход которого подключен к второму входу первого дополнительного элемента И, кроме того выход дополнительного формирователя импульсов через дополнительный инвертор подключен к первым входам второго и третьего дополнительных элементов И, выходы которых подключены соответственно к второму входу триггера управления и второму входу элемента ИЛИ, причем

HB В Гэрые входы Tplll ср!! Па -!л Ги в f )рого

6(363 78

Составитель И. Тюрин

Редактор Г, Антонов Техред.H. Аидрейчук Коррекч=р H. Ковалева

Заказ 2570/45 Тираж 815 Подписное

Ш1ИИИПИ 1асударственного комитета Совета Министров СССР но дела и изобретений и откры гпй

113035. Москва, Ж-35, Раушская наб., д. 4/5! илиал П11П "11 . òñûò, r. Ужгород, ул. Про вктная, 4 и третьего дополнительных элементов И поданы соответственно сигналы "коррекция", "исключение импул сов" и добавление импульсов".

И сточ tl ики информации, ц11и н ят ни ВО вни» мание при экспертизе:

1. Авторское свидетельство СССР

% 175082 МКИ 2 Н 04 ). 7/04, 106 3.