Устройство цикловой синхронизации

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТЬУ (»> 566379 (61) Дополнительное к авт. саид-ву (22) Заявлено22.12.75 (21) 2301308/09 (51) М. Кл.

Н 04 4 7/04 с присоединением заявки №Гасударственный квинтет

Совета Мнннетрав СССР ев деяам изобретений и открытий (23) Приоритет (43) Опубликоваид25.07.77.Бюллетень №27 (53) УДК 621.394. .662.2 (088.8) (4б) Дата опубликования описания08.08.77 (72) Авторы изобретения

А. А. Пыжов, В. 3. Ханин, В. С. Миронов, А, Ф. Толочко и А. В. Беланович

r )il)P (71) Заявитель

I (54) УСТРОЙСТВО ЦИКПОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к передаче дискретной информапии и может использоваться при построении аппаратуры передачи данных.

Известно устройство цикловой синхронизации, содержащее последовательно соединенные ключ, к первому входу которого подключен первый вход блока сравнения, ко второму входу ключа подключен первый выход регистра сдвига, к третьему входу клю- 0 ча подключен выход счетчика числа совпадений, к четвертому входу ключа подключен выход первого элемента И, регистр сдвига, дешифратор и первый элемент И, ко второму входу которого подключен выход тригге- 15 ра, к первому входу которого подключен выход первого элемента И, а ко второму входу триггера подключен через .счетчик чи .ла совпадений выход блока сравнения, ко второму входу которого подключен пер- р вый выход регистра сдвига (11.

Однако известное устройство обладает недостаточной точностью пикловой синхронизации 25

Цель изобретения — повышение точности цикловой синхронизации.

Это достигается тем, что в устройство цикловой синхронизации, содержащее последовательно соединенные ключ, к первому входу которого подключен первый вход блока сравнения, к второму входу ключа подключен первый выход регистра сдвига, к третьему входу ключа подключен выход счетчика числа совпадений, к четвертому входу ключа подключен выход первого элемента

И, регистр сдвига, дешифратор и первый элемент И, к второму входу которого подключен выход триггера, к первому входу которого подключен выход первого элемента

И, а к второму входу триггера подключен через счетчик числа совпадений выход блока сравнения, к второму входу которого подключен первый выход регистра сдвига, введены второй элемент И, декодер и блок памяти состояния декодера, при этом, выход декодера подключен через блок памяти состояния декодера к первому входу второго элемента И, к второму входу которого подключен выход первого элемента И, а вход декодера подключен к первому входу блока сравнения..

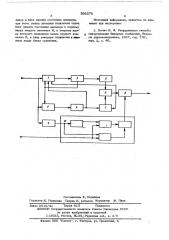

На чертеже изображена структурная электрическая схема предложенного устройства, Устройство содержит последовательно соединенные ключ 1, к первому входу которого подключен первый вход блока 2 сравнения, к второму входу ключа 1 подключен первый выход регистра 3 сдвига, к третье;му входу ключа 1 подключен выход счетчи- щ ка 4 числа совпадений, к четвертому входу клкяа 1 подключен выход первого элемента

И 8, регистр сдвига 3, дешифратор 6. Ко второму входу первого элемента И 5 подключен выход триггера 7, к первому входу которого подключен выход первого элемента И 5, а к второму входу триггера 7 подключен через счетчик 4 числа совпадений выход блока 2 сравнения, к второму входу которого подключен первый выход регистра сдвига 3. Устройство содержит также второй эа мент И 8, декодер 9 н блок 10 памяти состояния декодера, при этом выход декодера подключен через блок 10 памяти к первому входу второго элемента И 8, к второму вхо,25 ду которого подключен выход первого элемента И 5, а вход декодера 9 подключен к первому входу блока сравнения 2.

Устройство работает следующим образом. ,30

Информация, принимаемая из канала связи„ по входу поступает на блок 2 сравнения и через ключ 1 — на регистр сдвига 3., Количество поразрядных совпадений эталонной и принимаемой комбинации подсчитывается 35 счетчиком 4 числа совпадений.

В случае неудовлетворения хотя бы одной проверки счетчик 4 числа совпадений автоматически сбрасывается до нуля, н анализ начинается сначала. При наличии подряд 40

К-кратного совпадения счетчик 4 числа совпадений переводит регистр сдвига 3 через ключ 1 на автономную работу замыкая обратную связь регистра, и одновременно отключается поступление входной информаци- 45 онной последовательности на регистр сдвига 3.

Выделение фазирующего сигнала дешифратором 6 происходит при достижении комбинации на регистре сдвига 3 окончания фа+ О зового пуска. Фазирующий сигнал с д шьуратора, 6 через первый элемент И 5 при наличии сигнала с триггера 7, который взводится счетчиком 4 числа совпадений, поступает на ключ 1, размы ая обратную связь регистра сдвига 3 и подключая на вход регистра входную информацию, а также сбрасывает триггер 7 в исходное положение.

Фазирующий сигнал с выхода первого элемен. та И 5 поступает на второй элемент И 8.

Информация со входа поступает также на декодер 9, который выполняется по известным схемам, кодирования. Так как при передаче информации синхронизируюшая последовательность не кодир;ется, то на приеме декодер 9 при выделении истинной посылки синхронизации .сегда выдает сигкал о неправильно принятой кодовой комбинации, который через блок 10 памяти состояния декодера выдаст разрешение второму элементу И 8 на прохождение посылки синхронизации на выход устройства. Если фазирующая комбинация была выделена из информационной, то на выходе декодера 9 выделится, сигнал с правильно принятой кодовой комби, нации (прохождение по коду, так как на пе редаче кодовые комбинации кодируются), коt торый через блок памяти 10 состояния де,кодера запрещает второму элементу И 8 прохождение выделенной посылки синхрони| зации на выход устройства, чем исключает ее выделение из передаваемой информации.

Использование второго элемента совпадения, декодера и блока памяти состояния, декодера с соответствующими связями выI oéíî отличает устройство цикловой синхронизации от известного устройства, так как ве; роятность вьщеления синхронизирующей по, следовательности из инофмационной умень шается до нуля. В результате повышается точность цикловой синхронизации за счет устранения сбоев от случайного вьщеления

:синхронизирующей последовательности из информационной, что приводит к увеличению, пропускной способности канала связи и не . накладывает ограничение на передаваемую информацию.

Формула изобретения

Устройство цикловой синхронизации, содержащее последовательно соединенные ключ,,к первому входу которого подключен первый

; вход блока сравнения, к второму входу клю ча подключен первый выход регистра сдвн1

i га, к третьему входу ключа подключен вы, ход счетчика числа совпадений, к четверто, му входу ключа подключен выход первого

: элемента И, регистр сдвига, дешифратор и первый элемент И, к второму входу которого подключен выход триггера, к первому входу которого подключен выход первого, элемента И, а к второму входу триггера подключен через счетчик числа совпадений выход блока сравнения, к второму входу которого подключен первый выход регистра сдвига, о т л и ч а ю щ е е с я тем, что, с целью повышения точности цикловой син, хронизации, введены второй элемент И, де886379

Составитель Е. Погиблов

Редактор )Н. Разумова Техред И. Асталош Корректор jF. Папи

Заказ 2516/41 - Тираж 815 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб., д, 4/5 филиал ППП "Патент, r. Ужгород, ул. Проектная, 4

5 кодер и блок памяти состояния декодера, при этом, выход декодера подключен черее блок памяти состояния декодера к первому

t входу второго элемента И, к второму входу которого подключен выход первого элемента И, а вход декодера подключен к керн . вому входу блока сравнения.

Источникй информации, принятые во внимание при экспертизе:

1. Хомич И. Ф. Рекуррентные способы синхронизации бинарных сообщений, Вопросы радиоэлектроники,. 1967, сер. ТПС, вып. 2, с. 40.