Компенсационный стабилизатор напряжения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ пщ 567I67

Соки Советских

Социалистических

Реслублик (61) Дополнительное к авт. свид-ву 4995б1 (22) Заявлсно 12.04.76 (21) 2347736/07 с присоединением заявки № (23) Приоритет

Опубликовано 30.07.77. Бюллетень N 28

Дата опубликования описания 31,10.77 (5!) М. Кл.в 6 05F 1/56

Государственный комитет

Совета Министров СССР по делам кввбретеннй н открытий (53) УДК 621.316.722.1 (088.8) (72) Авторы изобретения (71) Заявитель

И. Д. Козицкий, В. И. Матвиив, Ю. В. Рево и Е. M. Шевчук

Специальное конструкторское бюро микроэлектроники в приборостроении (54) КОМПЕНСАЦИОННЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ

По основному авт. св. № 499561 известен компенсационный стабилизатор напряжения, содержащий два источника входного напряжения, один из которых соединен с выходом стабилизатора через последовательный регулирующий элемент, по цепи управления подключенный к выходу усилителя постоянного тока, один из входов которого подключен через источник опорного напряжения к общей точке стабилизатора, делитель выходного напряжения и усилительный транзистор, причем вывод питания усилителя постоянного тока соединен с выходом второго источника входного напряжения через дополнительный проходкой транзистор, при этом эмиттер последнего соединен с верхним плечом делителя напряжения на резисторах, средняя точка которого соединена с базой усилительного транзистора, нижнее плечо — с общей точкой, эмиттер усилительного транзистора соединен с выходом стабилизатора, а коллектор — с базой дополнительного проходного транзистора, вывод которого подключен ко втор ому источнику входного напряжения и к коллектору дополнительного проходного транзистора. Недостатком известного стабилизатора является отсутствие защиты стабилизатора от перегрузок по току.

Целью изобретения является обеспечение зашиты стабилизатора от перегрузок по току. Эта цель достигае.ся тем, что компенсационный стабилизатор напряжения снабжен транзисторно-резистивной цепочкой с дополнительным резистивным делителем напряже5 ния, причем резистор ускоряющей цепочки подключен между выходом усилителя постоянного тока и управляющим входом основного проходного транзистора, а транзистор коллектором соединен с управляющим входом основ10 ного проходного транзистора, эмиттером — c выходным силовым выводом основного проходного транзистора и базой — с выходом дополнительного резистивного делителя напряжения, включенного между входным силовым

16 выводом дополнительного проходного транзистора и общей шиной.

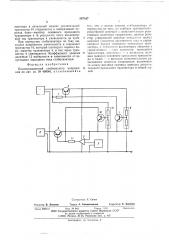

Функциональная схема компенсационного стабилизатора напряжения представлена на чертеже.

20 Стабилизатор содержит усилительный транзистор 1, дополнительный проходной транзистор 2, усилитель постоянного тока 3, основной проходной транзистор 4, источник опорного напряжения 5, делитель выходного напря25 жения б, нагрузочный резистор 7, основной источник входного напряжения 8, дополнительный источник входного напряжения 9 и ускоряющую цепочку на транзисторе 10, резисторе 11 и дополнительном резистивном де30 лителе напряжения 12.

При коротком замыкании на выходе стабиСоставитель С. Ситко

Техред А. Камышникова

Корректор Е. Хмелева

Редактор В. Левитов

Подписное

Заказ 2800/11 Изд. № 649 Тираж 1109

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 лизатора в начальный момент усилительный транзистор 10 открывается и закорачивает переход база — эмиттер основного проходного транзистора 4. В результате этого коллекторный ток транзистора 4 уменьшается до нуля.

При перетрузке стабилизатора по току выходное напряжение уменьшается и открывает транзистор 10, который шунтирует переход база — эмиттер транзистора 4, и ток через транзистор 4 уменышается, Коэффициент деления делителя 12 выбирается.в зависимости отдопустимого выходного тока стабилизатора.

Формула изобретения

Компенсационный стабилизатор напряжения по авт. св. № 499561, отличающийся тем, что, с целью защиты стаоилизатора от перегрузок по току, оп снабжен транзисторнорезнстивной цепочкой с дополнительным резистивныM делителем напряжения, причем резистор ускоряющей цепочки подклю ":í между выходом усилителя постоянного тока и управляющим входом основного проходного транЗИСтОРа, а тгаН"-1.СТОР КОЛЛЕКТОРОМ СОЕДИНЕН С управляющим ..;)ëîì основного проходного

10 транзистора, эмиттером — с выходным силовым выводом основного проходного транзистора и базой — с выходом дополнительного резистивного делителя напряжения, включенного между входным силовым выводом дополни15 тельного проходного транзистора и общей шиной.