Постоянное запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

О П И С А Н И Е }}}} завоет.

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-вуг (51) M. Кл.

5 11 С 17/00

5 11 С 29/00 (22) Заявлено03.02.75 (21) 2101569/24 с присоединением заявки №

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (23) Приоритет (43) Опубликовано06.08.77.Бюллетень № 29 (45) Дата опубликования описания,29.08.77 (53) УДК 681.327.6 (088.8) Р. С. Алумян, А. N. Иванов, Л. Ж. Гаспарян и Л. О. Ваганян (72) Авторы изобретения (71) Заявитель (54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

С САМОКОНТРОЛЕМ

Изобретение относится к запоминающим устройствам.

Известны постоянные запоминающие устройства 1ч,f2), например устройство, содержащее дешифратор адреса, выходы кото- 5 рого подключены с помощью элементов св . зи к группам выходных шин, соединенным с шифратором(1) ° Недостатками этого усч ройства являются низкая надежность и боль шие аппаратурные затраты. l0

Наиболее близким техническим -решением к предложенному является постоянное запоминающее устройство с самоконтролем (21, содержащее дешифратор адреса, выходы которого подключены к накопителю, состояще- 15 му изттт запоминающих блоков и Щ шифра-. торов, выходы которых соединены со входами тт »разрядного регистра числа, а вхо ды- - c выходами соответствующих запоминающих блоков, и элементы "И". 20

В этом устройстве запись информации ведется, геометрическими кодами, причем один запоминающий элемент хранит не один разряд кодовой комбинации, а всю кодовую комбинацию или ее часть (число разрядов 25

2 кодовой комбинации зависит от разрядности шифратора). В связи с. этим одиночная ошиб»ка в накопителе может привести к двойной, тройной и т. д. ошибке на выходах шифратора, которая не. будет обнаруживаться с вероятностью "1 и, следовательно, не будет исправляться. Это снижает надежность уст ройства.

Целью изобретения является повышение надежности постоянного запоминающего уст ройства.

Иоставленная цель достигается тем, что устройство содержитт}/тп сумматоров по мо дулю два и тп блоков контроля, входы кото» рых подключены к выходам соответствующих запоминаю:чих блоков, а выходы к одним входам элементов И", другие входы которых соединены с выходами сумматоров по модулто два. Выходы элементов И" под ключены. к счетным входам тт. - разрядного регистра числа, входы сумматоров по моду» лю два соединены с соответствующими вье-, ходами шифраторов.

568081

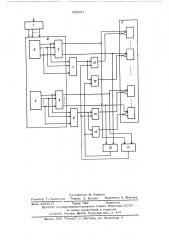

На чертеже дана блок-схема предложенного постоянного запоминающего устройства с самоконтролем (например, 2) .

Устройство содержит дешифратор адреса 1, накопитель 2, состоящий из запоминающих блоков Э и 4 и шифраторов 5 и 6, блоки контроля 7 и 8, и - разрядный регистр числа 9, сумматоры 10 и ll по модулю два, элементы И" 12»15, Выходы дешифратора адреса 1 подклю чены к накопителю 2, выходы запоминающих блоков 3, 4 — к входам шифраторов 5, 6 и блоков контроля 7, 8. Выходы шифраторов 5, 6 подключены к входам регистра числа 9 и сумматоров по модулю два 10, 11. Въ ходы блоков контроля 7, 8 подключены R одним входам элементов И 12-18, др>ъие входы которых соединены с выходами сумматоров по модулю два 10,- 11, Выходы элементов "И" 12 15 подключены к счетным входам регистра числа 9.

Постоянное запоминающее устройство при отсутствии ошибки работает следующим об разом, На вход дешифратора адреса 1 поо . тупает код адреса, который возбуждает один из выходов дешифратора адреса, а затем - один иэ выходов запоминающих блоков 3, 4 накопителя 2. На выходах шифраторов 5 8 образуются двоичные кодовые комбинации, которые записываются в регистр ре числа 9. На выходах блоков 7, 8 и сумма . торов по модулю два 10, 11 нет сигнала, так как в устройстве нет ошибки.

При наличии одиночной ошибки запом нающее устройство работает следующим об

35 разом. Пусть ошибка произошла в запоминающем блоке 3. Тогда блок контроля 7 вью» дает сигнал ошибки. Одновременно выдает сигнал ошибки, например, сумматор по модулю два 10. Открывается элемент И"

13 и соответствующий разряд регистра чис ла 9 исправляется.

Формула изобретения

Постоянное запоминающее устройство с самоконтролем, содержащее дешифратор адреса, выходы которого подключены к накопителю, состоящему иэ Фп запоминающих блоков и tn шифраторов, выходы которых соединены со входами И - разрядного регистра числа, а входы - с выходами соо ветствуюших запоминающих блоков, и элементы "И", о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройся ва, оно содержите/щ сумматоров по моду-, лю два и Фл блоков контроля, входы которых подключены к выходам соответствующих запоминающих блоков, а выходы K одним входам элементов "И, другие входы ко торых соединены с выходами сумматоров по модулю два, выходы элементов "И под ключены к счетным входам Ф - разрядного регистра числа, входы сумматоров по мо- дулю два соединены с соответствующими выходами шифраторов.

Источники информации, принятые во внимание при экспертизе:

Х-. Патент США М 3 653 004, кл, 340173, 1972.

2. "Известия ВУЗов СССР. Приборострое ние, т. 14, % 6, 1971, стр. 73-79 (прсо тотип).

568081

Составитель В. Рудаков

Редактор Т. Орловская Техред,A. Богдан Корректор A. Жолтани

Заказ 2808/37 Тираж 729 Подписное

Ш1ИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4