Устройство для контроля состояния канала связи

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (11) с (Я 17 О (61) Дополнительное к авт. <»«В Xì 53 3448 (22) Заявлено 04.01.76 (21) 2311653/09 с присоединением заявки №(23) Приоритет (43) Опубликоваио05,08.77»Бюллетень № 29 (45) Дата опубликования описания 19,09.77 (51) М. Кл.

Н 04 В 3/46

Государственный ноинтет

Венето Мнннстроо CCCP оо делаы нзооретеннй н открытнй

{5З) УДК 621.395.666 (088.8) (72) Автор изобретения

П. П. Жигора (71) Заявитель (54) УС И ОйСЧВО ДЛЯ КОНт1.ОЛЯ,СОСТОЯНИЯ

КАНАЛА СВЯЗИ

Изобретение относится к радиотехнике,,может использоваться для контроля каналов связи с переменными параметрами.

По основному авт.св. М 537448 иэвестло устройство для контроли состояния кана- 5 ета связи содержашее когерентный корреляционный приемник бинарных сигналов, две спусковые. схемы с автоматически регулируемым порогом, два элемента совпадения, два счет чика, интегратор, элемент сравнения, элементто

ИЛИ, счетчик интервалов, два элемента запрета, сдвиговый регистр, триггер, формирователь импульсов и разрядный счетчик 11).

Однако известное устройство не позволяет оценивать статистику пакетов сигналов не- 15 надежного обнаружения (CHG), что снижает точность контроля.

Hemü изобретения - повышение точности контр оля.

Для этого в устройство для контроля 20 состояния канала связи, содержащее когерентный корреляционный приемник бинарных сигналов, две спусковые схемы с автоматически регулируемым порогом, два элемента сов- . падения, два счетчика, интегратор, элемент я5 сравнения, элемент ИЛИ, счетчик интервалов, два элемента запрета, сдвиговый регистр, триггер, формирователь импульсов и разрядный счетчик, введены последовательно соединенные делитель частоты, управляюший счетчик, два элемента задержки, вход первого иэ ко торых соединен также с первыми входами вновь введенных соответствуюших ключей, блок считывания, блок счетчиков импульсов, дешифратор, блок элементов ИЛИ, выходы которого подключены ко . вторым в циам соответствующих ключей, Bblxop формирователя импульсов подключен ко второму входу разрядного счетчика через второй элемент задержки, а ко входу сброс блока счнтыЪания непосредственно, причем на вход делителя частоты подаются тактовые импульсы

{ти).

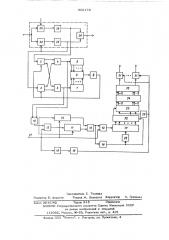

На чертеже приведена структурная электрическаяя схем а ус тр ойс тв а.

Устройство для контроля состояния канала связи содержит когерентный корреляционный приемник 1 бинарных сигналов, две спусковые схемы 2,3, два элемента совпадения

4,5, два счетчика 6,7, интегратор 8, эле-.

568170 мент сравнения 8, элеменг ИЛИ 10, счет чик 11 интервалов, два элемента запрета

12, 13, сдвиговый регистр 14, григгер 15,формировагель 16 импульсов, разрядный счетчик 17 последовательно соединенные делитель часго-, g ты 18, управляющий счетчик 10, элемент задержки 20, вход которого соединен также с первыми входами ключей 21, блок считывания 22, блок 23 счетчиков импульсов, дешифратор 24, блок 25 элементов ИЛИ, выходы которого подключены ко вторым входам соответствующих ключей 21; выход формирователя 16 импульсов подключен ко второму входу разрядного счетчика 17 через элемент задержки 26 и ко входу

"c5poc блока считывания 22 непосредственно, причем на вход делителя частоты 18 подаются ТИ со входа 27. Приемник 1 содержит умножители 28, интеграторы 29 и элемент сравнения 30. 20

Работает устройство следующим образом.

На вход устройства поступают полезный сигнал и помеха. В умножителях 28 зашумленный сигнал умножается на эталон- 25 ные единичный и нулевой сигналы. Случайные величины с интеграторов 29 поступают на спусковые схемы 2,3. Если эти сигналы больше порога, на единичных выходах спусковых схем 2,3 появляются car ЗО налы, поступающие на элемент совпаде ния 4, с которого на элемент ИЛИ 10 поступают CHO первого рода. Если сигналы на входах спусковых схем 2 и 3 меньше пс рога, на нулевых выходах их появляются сигналы, которые поступают на элемент совпадения 5, с которого на элемент ИЛИ

10 поступают СНО второго рода. Появившийся на выходе элемента ИЛИ 10 сигнал поступает на запрещающий вход элемен- 4О га запрета 12, тем самым запрещая прохождение ТИ со входа 27 на счетчик 11.

Кроме того, э.гог же СНО поступает на сдвиговый регистр 14 и на вход сброс" счетчика 11, который тем самым устанав- 4> ливается в нулевое" состояние.

Если на следующем такте работы усгройст ва на запрещающий вход элемента запрета

12 не поступает СНО, на счетчик 11 проходит первый ТИ. На следующем такте, если на выхода элемента ИЛИ 10 нет СНО на счетчик 11 поступаег второй ТИ и т.д. до тех пор, пока на выходе элемента ИЛИ 10 не появится имгульс СНО. Через 3С „гакгов после появления на выходе элемейга

ИЛИ 10 первого импульса CHO атог импульс появляется на выходе сдвигового регистра

14 и поступает на нулевой вход триггера 15, который переходит из единичного в нулевое состояние, и потенциал на запрещаюшем @р вхопе элемента запрета 13 исчезает. Через элеменг запрета 13 на разрядный счет чик 17 проходит ТИ, На X>a.g +1-вом гакге, если .за это время импульсы СНО, кроме первого, не появились, на выходе счетчика

11 появляется сигнал, который поступает на единичный вход триггера 15, который переходит в единичное состояние. С триг гера 15 на запрещающий вход элемента запрета 13 поступает высокий потенциал, который запрещает, прохождение ТИ на разрядный счетчик 17.

Одновременно формирователь 16 по перепаду потенциалов на выходе триггера 15 формирует импульс, который устанавливает счетчик 17 в нулевое состояние.

Если интервал между первым и следующим за ним CHO не больше Х гактов, устройство работает следующим образом.

Первый импульс СНО через2Г3,1гактов появляется на выходе cgBBrQBQI регистра

14, поступает на нулевой вход триггера

15 и тереводит его в нулевое состояние. На выходе триггера 15 исчезает высокий потенциал, элемент запрета 13 открывается и на разрядный счетчик 17 проходит ТИ.

До появления сигнала через Ж о + 1 тактов на выходе счетчика на запрещающий вход элемента запрета 12 поступает второй СНО, который поступает также на сдвиговый регистр 14 и сбрасывает счетчик

1l в нулевое состояние. Если интервал между вторым и третьим CHO также меньше Хуту, сигнала на выходе счетчика 11 не появляется, и триггер 15 остается в нулевом состоянии. Через открытый элемент;запрета 13 все время проходят ТИ. Таким образом, до тех пор, пока интервал между поступающими с элемента ИЛИ 10 импульсами

СНО не больше. Х >, на элемент —. запрета 12 поступают СНО, принадлежащие одному и тому же пакету СНО некоторой длины, на разрядный счетчик 17 прохщят ТИ, и счетчик подсчитывает длину пакета.

Пусть на каком-либо такте на запрещающий вход элемента запрета 12 поступает последний СНО, принадлежащий данному пакету. Через Х>о тактов этот СНО появляет ся на выходе сдвигового регистра 14ипоступает на нулевой вход триггера 15. На счет чик 17 через открытый элемент запрета

13 поступает еще один ТИ, Так как рассмач риваемый СНΠ— последний в пакете, то интервал между ним и следующим CHO больше

Õ ó. Поэтому на следующем Х +1 -вом такте после поступлений .па элемент запрета

12 последнего CHO данного пакета на выходе счетчика 11 появляется импульс. Этот импульс посгупаег на единичный вход триггера 15 н переводит его в единичное сосгоя56817 0

6 ние. Па в»!xoäå триггера 15 появлябтся высс кий и отенциял к ОтophfA эдкрывле Г элемент запретя 13. Перепад потенциалов вызывает срабатывание формирователя 16, и с его выхода импульс поступает на управляющий вход блока считывания 22, а через элемент задержки 26 устанавливает разрядный счетчик 17 в нулевое состояние.

Таким образом, число ТИ, зафиксированное в разрядном счетчике 17, со ветует!0 длине пакета СНО. Ц зависимости от вели-. чины этого числа на одном из выходов блока считывания 22 появляется импульс, который заносится в блох 23 счетчиков импульсов.

В конце контрольного интервала, величиI на которого определяется коэффициентом деления делителя частоты 18 и емкостью. управляющего счетчика 19, по импульсу с последнего считывается содержимое блока

23. В зависимости or содержимого блока 232О на одном из выходов дешифратора 24 появляется сигнал, который через блок 25 поступает на соответствующий ключ 21.

В конце каждого контрольного интервала по сигналу управления с управляющего счет- д чика 19, подаваемому на первые входы ключей 21, на выходе одного из ключей появляется сигнал, подаваемый с сос тветствующего выхода блока 25, который сигнализирует о состоянии канала связи. Этим же сигналом с управляющего <:чг. тчяк л 1 9 через элемент задержки 20 блок 23 устно ливаетсн в нулевое состояние.

Формула изобретения

Устройство для контроля состояния к;— нала связи по авт. св. И 537448, о т л ичающее с я тем, что, с целью пжыщения точности контроля, в него введены последовательно соединенные делитель частоты, управляющий счетчик, два элемента задержки, вход первого из которых соединен также с первыми входами вновь введенных соответствующих ключей, блок считывания, блок ;счетчиков импульсов, дешифратор, блок элементов ИЛИ, выходы которого подключены ко вторым входам соответствукщих ключей, выход формирователя импульсов подключен ко второму входу разрядного счетчика через второй элемент задержки, а ко входу сброс блока считывания непосредственно, причем на вход делителя частоты подаются тактовые импульсы.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

Pk 537448 Н 04 В 3/46, 1974.

568170

Составитель Г. Теплова

Редактор Б. Федотов Техред М. Левицкаи Корректор А. Грииенко

Заказ 2816/42 Тираж 815 Подписное

ILHHHHH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектнаи, 4