Устройство для контроля последовательности чередования аналоговых сигналов

Иллюстрации

Показать всеРеферат

(6l) Дополнительное к авт. свил-ву (22) Заявлено 08.12.75 (21) 2300989l09

k (51) М. Хл.

Н 04 В 17/00 с присоединением заявки №Гвсударственннй кэинтет

Ссмта Мнннстрсв СКр

N днпзи мзссрстсннн н еткритнй (23) Приоритет (43) Опубликованд 05.08.77.бюллетень № 29 (45) Дата опубликования описания;20.09.77 (53) УДК 621.317.743 (088.8) В. С. Алешин и В. И. Дмитриев (72) Авторы изобретения (7т) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСЛЕДОВАТЕЛЬНОСТИ

ЧЕРЕДОВАНИЯ AHAllQMBblX СИГНАЛОВ

Изобретение относится к автоматике и вычислительной технике и может использоваться в автоматических устройствах контроля последовательности аналоговых сигна» лов. Ь

Известно устройство для контроля последовательности чередования аналоговых сигналов, включающее блок формирования сигнала ошибки, управляющий вход которого соединен с выходом триггера tl). l0

Однако это устройство не позволяет производить автоматический .контроль последовательностей аналоговых сигналов.

Бель изобретения - повышение точности контроля. и

Для этого в устройство для контроля последовательности чередования аналоговых сигналов, содержащее блок формирования сигнала ошибки, управляющий вход которс . го соединен с выходом триггера, введены 20 инвертор и блоки обработки аналогового сигнала, каждый нз которых состоит из последовательно соединенных первого элемента НЕ, первого элемента И, второгo ýëåìåHта HE u sroporo элемента И, при атом к 25

;каждому из входов блока,,формирсвания ,сигнала ошибки подключен соответствующий блок обработки аналогового сигнала, на управляющие входы элементов И которого подан входной аналоговый сигнал, причем выход второго элемента НЕ каждого блока об работки аналогового сигнала, кроме последнего, подключен ко входу первого элемента

НЕ последующего блока обработки аналого вого сигн ча, а выход второго элемента НЕ последнего блока обработки аналогового сигнала подключен через инвертор ко входу триггера.

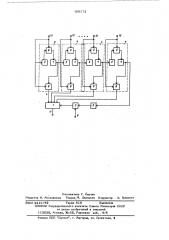

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство для контроля последовател ности чередования аналоговых . сигналов содержит блок 1 формирования сигнала ошибки, управляющий вход которого соединен с выходом триггера 2, инвертор З и блоки 4 ,обработки аналогового сигнала, каждый из которых состоит из последовательно соединен1 ,ных первого элеменга HL 5, первого алемен1та И 6 второго элемента НЕ 7 и второго ,элемента И 8, при pro» к каждому из входов

568 17 3. блока > формирования сигнала ошибки подклю. чен, с<югветсгвующий блок 4 обработки аналогового сигнала, на управляющие входы элемент И 6,8 которого подан входной аналоговый сигнал, причем выход второго элемен- 5 та НЕ каждого блока 4 обрабогки аналогового сигнала, кроме последнего, подключен ко входу первого элемента НЕ 5 последующего блока 4 обработки аналогового сигнала, а выход второго элемента НЕ 7 послед о него блока 4 обработки аналогового сигна.ла подключен через инвертор 3 к входу триг. гера 2.

Устройство работает следующим образом.

Перед началом цикла контроля разрешаю!

5 щим импульсом "сбрсс 8 триггер.2 перебрасывается в единичное состояние, при этом с блока 1 формирования сигнаш ошибки,снимается запирающее нулевое напряжение триггера Зе

ffpa поступлении на входы 10 устройства последовательности аналоговых . сигналов отирываетси соответствующий приходящему сигналу первый элемент И бм второй эле15 мбит И 8 блока 4 обработки аналогового сиг нала. Через первый элемент, И 6 выход пер.вого элемента HE подключается ко входу второго элемента НЕ, который меняет свое состояние. на единичное. При этом первый элемент И 6 последующего блока 4 обработки аиалогавого сигнала меняет свое состояние на нулевое. Таким образом производич ся последовательное изменение состояний баск<в обработки аналогового сигнала при

35 соблюдении заданной последовательности поступления аналоговых сигналов на входы

1Î. При этом высокие выходные напряжения блок я 4 обработки аналоговых сигналов, подключаемые к соответствующим входам

:бликса 1 формирования сигнала ошибки через свои вторые элементы И 8, не меняют состояния этого блока, и на выходе устройсгиа 11 по-прежнему остается низкий,уровень напряжения.

lips выпадении какого-либо сигнала на последовательности второй элемент НЕ 7 блсжа 4 обработки аналогового сигнала, иа котором гроизошло нарушение последовательности, не изменяет своего нулевого

50 сосгояния, а, следоватольно, первый элемент HB 5 последующего блока 4 обработ ии аналогового сигнала также сохраняет свое единичное состояние.

При этом обнаружение факта пропадания сигнала происходит в момент поступления на вход 10 любого последующего сигнала, при поступлении которого выходной низкий уровень напряжения соответствующего блока 4 обработки аналогового сигнала через второй элемент И 8 подключается к одному из входов блока 1 формирования сигнала ошибки, который вырабатывает сигнал ошибки. При этом на выходе 11 появляется вы- сокий уровень напряжения.

При поступлении на вход 10 сигнала и при условии соблюдения последовательности предыдуших аналоговых сигналов, инвергор

3 изменяет свое состояние на нулевое, что вызывает переброс триггера 2 в исходное . состояние, когорое сохраняется да наступления нового цикла контроля, Ф ормула изобре гения

Устройство для контроля последователь— ности чередования аналоговых сигналов, включающее блок формирования сигнала ошибки, управляющий вход которого соединен с выходом триггера, о т л и ч а ю щ е е с я тем, что, с целью повышения точности контроля, введены инвертор н блоки обработки аналогового сигнала, каждый из которых состоит нз последовательно соединенных первого элемента НЕ, первого элемента И,, второго элемента НЕ и второго элемента И, при эгом к каждому из входов блока формирсьвания сигнала ошибки подключен соответствующий блок обработки аналогового сигнала, на управляющие входы элементов И которого йодан входной аналоговый сигнал, причем выход второго елеменга НЕ каждого блока обрабогки аналогового сигнала, кроме последнего, подключен ко входу первого элеменга НЕ последующего блока обработки аналогового сигнала, а выход второго элемента НЕ последнего блока обработки аналогового сигнала подключен через ннвергор ко входу триггера.

Источники информации, принятые во внимание при экспертизе:

1. Авгорское свидетельство СССР

И 440665, МКн 6 06 V 11/00, 1972 э6817 3

Составитель Г. Серова

Редактор И. Маоховскаи Техред М. Левицкая Корректор, А. шипенко

I абакан 2816/42 Тираж 815 Подписное

ЦИИИПИ Государственного комитета Совета Министрсв СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., < 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4