Импульсный частотно-фазовой дискриминатор

Иллюстрации

Показать всеРеферат

(11) 569ООО

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (б1) Дополнительное к авт. свид-ву (22) Заявлено 04.10.74 (21) 2073693/21 с присоединением заявки М (23) Приоритет

Опубликовано 15.08.77. Бюллетень 1ч" 30

Дата опубликования описания 22.08.77 (51) М. Кл. H 03D 13/00

Государственный комитет

Совета Мннистров СССР ло делам изобретений и открытий (53) УДК 621.375.3 (088.8) (72) Автор изобретения и (71) заявитель

В. И. Стребков (54) ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР

Изобретение относится к импульсной технике.

Известен частотно-фазовый дискриминатор, содержащий входные логические элементы И, на входы которых поданы дискриминируемые сигналы, триггеры, входы которых через дополнительные логические элементы соединены с выходами входных элементов И, а выходы через соответствующие логические элементы

И, ИЛИ, НŠ— с входами входных элементов И (1).

Данный дискриминатор сложен.

Наиболее близким по технической сущности к заявленному является дискриминатор, содержащий два входных логических элемента И, один из входов каждого из которых подключен к источнику входных сигналов, а выход — к входу логического элемента ИЛИ, выходной триггер со счетным входом, который соединен с выходом второго логического элемента ИЛИ. Входы последнего соединены с выходами двух дополнительных логических элементов И, первые входы которых подключены к выходам соответствующих входных логических элементов И, а вторые входы — к выходам второго триггера, входом соединенного с выходом первого из упомянутых логических элементов ИЛИ (2).

Данный дискриминатор недостаточно надежен в работе при изменении параметров входных импульсов.

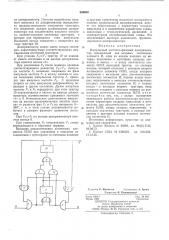

Целью изобретения является повышение надежности работы дискриминатора при изменении параметров входных импульсов. Это достигается в предлагаемом дискриминаторе тем, что в него введены два дополнительных логических элемента ИЛИ, входы которых подключены к выходам указанных триггеров, а выходы соединены с другими входами входных логических элементов И. тО Структурная электрическая схема дискриминатора приведена на чертеже.

Дискриминатор содержит логические элементы И 1 — 4, логические элементы ИЛИ

5 — 8, триггеры 9, 10. На входы 11 и 12 по15 даны дискриминируемые сигналы F, и F2, выходной сигнал снимается с выхода 13. Источники питания и сигналов на чертеже не показаны.

Принцип работы дискриминатора заключа20 ется в следующем.

На входы 11 и 12 элементов И 1 и 2 поступают импульсы с частотами соответственно

F> и F2. По вторым входам элементы 1, 2 управляются сигналами с выходов триггеров 9

25 и 10. Входные импульсы через логические элементы 1 — б поступают на счетные входы триггеров.

Триггеры переключаются при переходе сигналов на счетных входах от 0 до «1». Таким

30 образом, триггеры могут переключаться только после окончания импульса, поступающего

569000

Типография,пр. Сапунова, 2 на дискриминатор. Поэтому воздействие входного импульса на дискриминатор определяется предшествовавшим состоянием триггеров, что исключает ложное срабатывание дискриминатора под воздействием входного импульса, соответствующее состоянию триггеров, в которое они переводятся этим импульсом.

Выходной сигнал снимается с инверсного выхода триггера 10.

Дискриминатор может иметь четыре состояния, характеризуемые соответствующими комбинациями состояний триггеров.

При условии Р2(Р1 триггер 10 не изменяет своего состояния и на выходе дискриминатора имеется сигнал «1».

При увеличении F после момента времени, соответствующего равенству Fa —— Е,, импульсы частоты Fq начинают опережать по фазе импульсы частоты F> и между какими-то двумя соседними импульсами частоты F приходят два импульса частоты Ря. С приходом второго из этих импульсов дискриминатор переходит в другое состояние. Далее импульсы частоты г1 и Рв чередуются, при этом триггер

10 переключается и сигнал на выходе дискриминатора соответственно принимает значения

«1» и О. Относительная длительность импульсов на выходе дискриминатора линейно зависит от разности фаз Р1 и F2 на интервале О—

360, т. е. в этом случае дискриминатор ра- 30 ботает в режиме фазового сравнения сигналов.

При Fq)F> на выходе дискриминатора имеется сигнал О.

При уменьшении Рв относительно F> схема переключается в обратном порядке.

Введение дополнительных логических элементов ИЛИ при указанном в описании их соединении с триггерами со счетными входами и другими элементами исключает возможность ложных срабатываний дискриминатора, делает его некритичным к параметрам входных импульсов и к изменениям параметров схемы, связанным с технологической, временной и температурной нестабильностями схемы. Это обеспечивает высокую надежность функционирования дискриминатора.

Формула изобретения

Импульсный частотно-фазовый дискриминатор, содержащий два входных логических элемента И, один из входов каждого из которых подключен к источнику входных сигналов, а выход — к входу логического элемента ИЛИ, выходной триггер со счетным входом, который соединен с выходом второго логического элемента ИЛИ, входы которого соединены с выходами двух дополнительных логических элементов И, первые входы которых подключены к выходам соответствующих входных логических элементов И, а вторые входы — к выходам второго триггера, вход которого соединен с выходом первого из упомянутых логических элементов ИЛИ, отл ич а ю щи и ся тем, что, с целью повышения надежности работы дискриминатора при изменении параметров входных импульсов, в него введены два дополнительных логических элемента ИЛИ, входы которых подключены к выходам указанных триггеров, а выходы соединены с другими входами входных логических элементов И.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии ¹ 30584, кл. 98(5) Е32, 09.08,72.

2. Патент CLUA № 3386021, кл. 318-329, 10.12,66.

Редактор Р. Юрчикова Составитель А. Артюх

Корректор И. Позняковская

Заказ 1894i! Изд. № 695

Тираж 1080 Подписное

Ц11ИИПИ Государственного комитета

Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5