Управляемый цифровой делитель частоты для систем фазовой автоподстройки частоты

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 1а 5690 01

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистииеских

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 30.03.76 (21) 2339ll17/21 с присоединением заявки № (23) Приоритет

Опубликовано 15.08,77. Бюллетень № 30

Дата опубликования описания 22.08.77 (51) M. Кл е Н 03D 13/00 т осударственный комите

Совета Министров СССР по делам изобретений и открытии (53) УДК 621.375.3 (088.8) (72) Авторы изобретения

Я )Кук и В. E. Ершов (71) Заявитель (54) УПРАВЛЯЕМЫЙ ЦИФРОВОЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

ДЛЯ СИСТЕМ ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ

Изобретение относится к импульсной технике.

Известен делитель частоты импульсов с управляемым коэффициентом деления, состоящий из двух основных частей: делителя с целочисленным переменным коэффициентом деления (ДПКД) и программирующего устройства, в определенной последовательности изменяющего коэффициенты деления в различных циклах в процессе работы делителя. В результате при усреднении коэффициенты не равны целому числу. Такие делители используются при построении цифровых синтезаторов частот и предназначены для снижения уровня пульсаций опорного колебания в управляющем сигнале, а также повышения динамических свойств системы за счет увеличения частоты сравнения при сохранении малого шага дискретности частот выходного сигнала (1).

Однако у известных ДПКД минимальная дискретность приращения коэффициента деления в различных циклах деления равна единице.

Наиболее близким по технической сущности к данному изобретению является управляемый цифровой делитель частоты, содержащий делитель частоты с переменным коэффициентом деления, один вход которого соединен с выходом блока исключения импульсов, а выход соединен со входом блока программы, один выход которого подключен к первому входу блока исключения импульсов, второй вход которого соединен с источником

5 входного сигнала, а третий вход — со вторым выходом делителя частоты с переменным коэффициентом деления (2).

Недостатком такого делителя является малая дискретность изменения коэффициента де10 ления.

С целью увеличения дискретности изменения коэффициента деления в предлагаемый делитель частоты введен П(-триггер и управляемый инвертор, причем счетный вход

15 П(-триггера соединен с источником входного сигнала, I — входы соединены со вторым выходом делителя частоты с переменным коэффициентом деления, К вЂ” входы соединены со вторым выходом блока программ, причем вы20 ходы П(-триггера соединены с двумя входами управляемого инвертора, третий вход которого соединен с источником входного сигнала, а выход соединен со вторым входом делителя частоты с переменным коэффициентом деле25 ния.

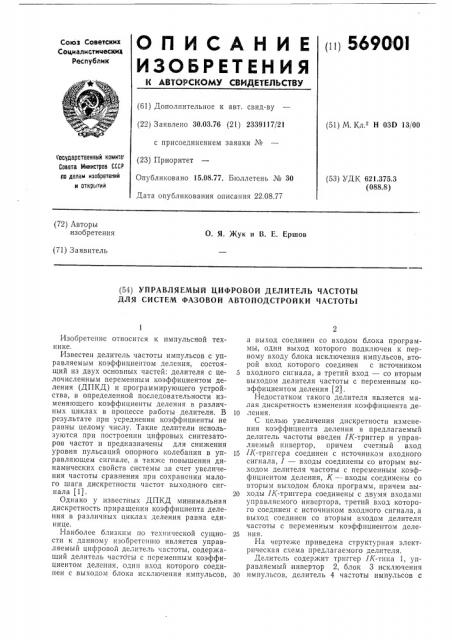

На чертеже приведена структурная электрическая схема предлагаемого делителя.

Делитель содержит триггер П(-типа 1, управляемый,инвертор 2, блок 3 исключения

50 импульсов, делитель 4 частоты импульсов с

569001

Составиз ель A. A!;-т ок

Текред М. Семенов

Корректор И. Позняковская

Редактор Н. Каменская

Заказ 1894/2 Изд. № 695 Тираж 1080 11одппсное

ЦНИИПИ Государственного комитета Совета М нгнстров СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раугнская наб., д. 4/5

Типография, пр. Сапунова, 2 переменным коэффициентом деления (ДПКД), блок 5 программ. 1-1а вход 6 подается сигнал делимой частоты, выходной сигнал снимается с выхода 7 (источники сигналов и питания на схеме не показаны).

Принцип работы делителя заключается в следующем.

Выходной сигнал делителя 4 поступает на вход блока 5, состоящего из последовательно соединенных пятеричного счетчика для получения десятых долей и декадных счетчиков (не показаны), количество которых соответствует количеству младших дробных разрядов.

Блок программы 5 формирует необходимую программу, которая выбирается внешними органами управления (не показаны).

Блок 3 при наличии сигнала о заполнении делителя 4 и разрешающего сигнала с блока

5 производит блокировку делителя 4 на один период входной последовательности, т. е. увеличивает коэффициент деления в данном рабочем цикле на единицу. Триггер 1 при наличии разрешающих сигналов с приходом очередного тактового импульса меняет свое состояние на противоположное и на делитель 4 поступает инвертированный сигнал.

В результате инверсии делитель 4 срабатывает на второй импульс, который сдвинут на полтакта относительно исходного неинвертированного сигнала, это соответствует увеличению коэффициента деления на 0,5. Для получения коэффициента N на блок 3 и триггер

1 поступают запрещающие сигналы с блока

5, для получения коэффициента N+0,5 срабатывает одновременно блок 3 и триггер 1 и, наконец, для получения коэффициента

/у +1 работает только блок 3, Формула изобретения

Управляемыи цифровои делитель частоты для систем фазовой автоподстройки частоты, содержащий делитель частоты с переменным коэффициентом деления, один вход которого соединен с выходом блока исключения им10 пульсов, а выход соединен со входом блока программы, один выход которого подключен к первому входу блока исключения импульсов, второй вход которого соединен с источником входного сигнала, а третий вход — со

15 вторым выходом делителя частоты с переменным коэффициентом деления, о т л и ч а юшийся тем, что, с целью увеличения дискретности изменения коэффициента деления, в него введен П(-триггер и управляемый инвер20 тор, причем счетный вход П(-триггера соединен с источником входного сигнала, I — входы соединены со вторым выходом делителя частоты с переменным коэффициентом деления, /(— входы соединены со вторым выходом блока программ, причем выходы //(-триггера соединены с двумя входами управляемого инвертора, третий вход которого соединен с источником входного сигнала, а выход соединен со вторым входом делителя частоты с переменным коэффициентом деления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР К 344590, кл. Н 03D 13/00, 19б9.

35 2. Патент США Ао 32172б7, кл. 331 — 1б, 19б8.