Фазовый синхронизатор

Иллюстрации

Показать всеРеферат

<>569938

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 27.06.75 (21) 2148745i09 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 15.08.77. Бюллетень ¹ 30 (45) Дата опубликования описания 28.!1.77 (51).ц1 1;,ь H 04 L 7/02

Государственный комитет

Совета Министров СССР по делам изобретений и OTKpblTHN (53) УДК 621.394.662 (088.8) (72) Автор изобретения

Н. С. Лобов (71) Заявитель (54) ФАЗОВЫЙ СИНХРОНИЗАТОР

Изобретение относится к технике телеграфной связи и может быть использовано в дешифраторах при приеме частотной телеграф,ии.

Известен фазовый синхронизатор, содержащий последовательно соединенные формирователь импульсов, блок добавления-вычитания импульсов и делитель частоты, а также формирователь импульсов разрешения добавления и формирователь импульсов разрешения вычитания, первые выходы которых подключены к соответствующим входам блока добавления-вычитания импульсов, причем вторые выходы формирователя импульсов и формирователя импульсов разрешения вычитания подключены ко входам элемента и (1).

Однако известный фазовый синхронизатор не обеспечивает необходимой помехоустойчивости при расширении полосы синхронизации.

С целью повышения помехоустойчивости при расширении полосы синхронизации в предлагаемый фазовый синхронизатор введены формирователь сигнала с нулевой зоной и дополнительный формирователь импульсов разрешения добавления, при этом выходы разрядов и основной выход делителя частоты подключены к соответствующим входам формирователя сигнала с нулевой зоной, один из выходов которого подключен к соответствующим входам формирователя импульсов разрещения вычитания и формирователя импульсов разрешения добавления, а другой выход подключен к соответствующему входу дополнительного формирователя импульсов разрешения добавления, ко второму входу которого подключен дополнительный вход формирователя импульсов разрешения добавления, а выход допоlHèòåëbHîãо формирователя импульсов разрешения добавления .подключен к !

О дополнительному входу блока добавлениявычитания импульсов.

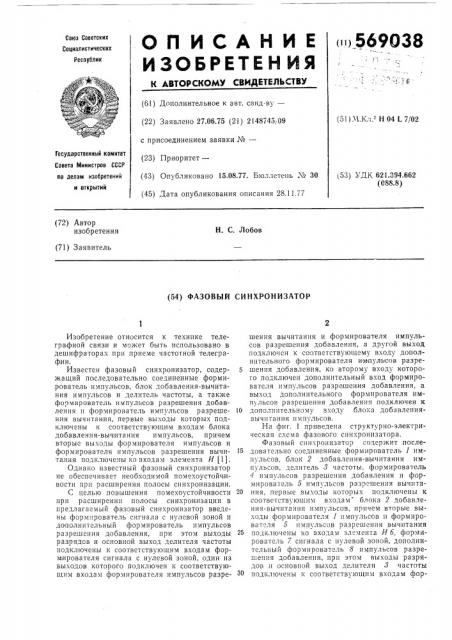

На фиг. 1 приведена структурно-электрическая схема фазового синхронизатора.

Фазовый синхронизатор содержит после-!

5 довательно соединенные формирователь 1 импульсов, блок 2 добавления-вычитания импульсов, делитель 8 частоты., формирователь

4 импульсов разрешения добавления и формирователь 5 импульсов разрешения вычпта20 ния, первые выходы которых подключены к ссответствующим входам блока 2 добавления-вычитания импульсов, причем вторые выходы формирователя 1 пмптульсов и формирователя 5 импульсов разрешения вычитания

25 подк,1ючены ко входам элемента 0 б, формирователь 7 сигнала с нулевой зоной, дополнительный формирователь 8 импульсов разрешения добавления, при этом выходы разрядов .и основной выход делителя 8 частоты подключены к соответствующим входам фор569038 мирователя 7 сигнала с нулевой зоной, один из выходов которого подключен к соответствующим входам формирователя 5 импульсов разрешения вычитания и формирователя 4 импульсов разрешения добавления, а другой выход подключен к соответствующему входу дополнительного формирователя 8 импульсов разрешения дооавления, ко второму входу которого подключен дополнительный вход формпрсвателя 4 импульсов разрешения добавления, а выход дополнительного формирователя 8 импульсов разрешения добавления подключен к дополнительному входу блока 2 добавления-вычитания импульсов.

Фазовьш синхронизатор работает следующим ооразом.

На формирователь 1 .импульсов подаются имп1 I chI I Ic roToA n („, (n — :.Оэффициент деления делителя 8 частоты), сдвинуTbIc Один DTIIocнтсльно другого на половин периода. Эти импульсы поступают на блок 2 дооавления-вычитания импульсов, элемент Иб и делитель 8 частоты. Н3 выхо;1е послед .Ip.ro возникают импульсы с частотой, приблизительно равной f из которы.: формирователем 7 сигнала с нулевой зоной формируется сигнал с нулевой зоной. Этп импульсы создают нулевую зону при синфазности. В отрицательные перепады промежуточной частоты через формирователь 5 импульсов разрешения вычитания выдается сигнал, запрещающий прохохк icIIHc,импульсов на делитель 8 частоты через блок 2 добавления-вычитания импульсов. Фаза импульсов с делителя 8 частоты отстает на вели шну ширины импульсов. Импульс разрешения вычитания формируется постоянно при f„„(f подставки.

При f. (f подставки фазовый синхронизатор работает следующим образом.

Импульсы сигнала f „„поступают на формирователь 4 импульсов разрешения добавления, который формирует импульсы от положительных и отрицательных фронтов сигнала.

Импульс, соответствующий отрицательному фронту, поступает на формирователь 4 импульсов разрешения добавления при отрицательном перепаде импульсов, который формирует импульс разрешения добавления. Импульс разрешения добавления через блок 2 добавления-вычитания импульсов поступает на делитель 3 частоты, а с него импульсы укорачиваются и положительным перепадом перебрасывают формирователь 5 импульсов разрешения вычитания в исходное состояние.

Импульсы добавления и импульсы вычитания с элемента Об поступают на выход синхронизатора для формирования полярности посылки в зависимости от поступающей на вход частоты сигнала. С целью увеличения полосы синхронизации при f„ f подставки дополнительно введены формирователь 7 сигнала с нулевой зоной и дополнительный формирователь 8 импульсов разрешения добавления.

Второй метод увеличения полосы синхрониза10 ции — это увеличение частоты импульсов добавления.

Формула изобретения

Фазовый синхронизатор, содержащий последовательно соединенные формирователь импульсов, блок добавления-вычитания импульсов и делитель частоты, а также форми20 рователь импульсов разрешения добавления и формирователь импульсов разрешения вычитания, первые выходы которых подключены к соответствующим входам блока добавления-вычитания импульсов, причем вторые

25 выходы формирователя импульсов и формирователя импульсов разрешения вычитания подключены ко входам элемента И, о т л ич а ю шийся тем, что, с целью повышения помехоустойчивости при расширении полосы

З0 синхронизации, введены формирователь сигнала с нулевой зоной и дополнительный формирователь импульсоз разрешения добавления, при этом выходы разрядов и основной выход делителя частоты подключены к соответствующим входам формирователя сигнала с нулевой зоной, один нз выходов которого подключен к соответствующим входам формирователя импульсов разрешения вычитания и формирователя импульсов разрешения до40 бавления, а другой выход подключен к соответству1ощему входу дополнительного формирователя импульсов разрешения добавления, ко второму входу которого подключен дополнительный вход формиро вателя импульсов разрешения добавления, а выход дополнительного формирователя импульсов разрешения добавления подключен к дополнительному входу блока добавления-вычита ния ими ульсо,в.

Источник информации, принятый во внимание при экспертизе изобретения:

1, Е. М. Мартынов, Синхронизация в системах передачи дискретных сообщений, М., 55 «Связь», 1972, с. 110.

569038

Составитель Л. Каграманова

Техред М. Семенов Корректор И. Симкина

Редактор Т. Янова

Тип. Харьк. фил. пред. «Патент»

Заказ 648/1824 Изд. Мо 6Я Тираж 818 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, K-35, Раушская наб., д. 4/5