Устройство для приема дискретной информации в системах с решающей обратной связью

Иллюстрации

Показать всеРеферат

ОП ИСАНРЕ

ИЗОБРЕТЕН ЙЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 23.02.76 (21) 2335459,l09 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 15.08.77. Бюллетень № 30 (45) Дата опубликования описания 01.11.77 (51) М.Кл. Н 04 L 17/16

Государственный ком ите r

Совета Министров СССР по делам изобретений н открытии (53) УДК 621.394.14 (088.8) (72) Авторы изобретения

В. П. Афанасьев и Ю. Д. Рысков (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРИЕМА

ДИСКРЕТНОЙ ИНФОРМАЦИИ В СИСТЕМАХ

С РЕШАЮЩЕЙ ОБРАТНОЙ СВЯЗЬЮ

Изобретение относится к технике передачи данных и может использоваться для защиты аппаратуры передачи данных с решающей обратной связью от вставок и выпадений информации.

Известно устройство для приема дискретной информации, в системах с решающей обратной связью, содержащее согласующий блок, выход которо1-о подключен к входач накопителя, блока сравнения циклических 10 номеров, декодера и приемника сигнала «Фаза», причем выходы блока сравнения цикл",ческих номеров и приемника сигнала «Фаза» через последовательно соединенные первый элемент ИЛИ, первый элемент И, второй элемент ИЛИ, к второму входу которого подключен выход декодера, и второй элемеHT И подключены к входу регистра блокировки, тактовый выход которого подключен к второму входу второго элемента И непосредственно, а к входам блока сравнения циклических номеров и блока сопряжения соответственно через датчик циклических номеров и накопитель (1)25

Однако в известном устройстве необходимость вмешательства оператора при трансформации сигнала «Запрос» в сигнал «Подтверждение» уменьшает скорость передачи информации и препятствует использованию аппаратуры в автоматизированной систем управления.

С целью сокращения времени на исключение вставок и выпадений при приеме информации в предлагаемое устройство для приема дискретной информации в системах с решающей обратной связью введены решающий блок, блок задержки, формирователь сигнала «Ошибка», два дополнительных элемен га

И и дополнительный элемент ИЛИ, при этом выход декодера и вход регистра блокировки подключены к соответствующим входам первого дополнительного элемента И, выход регистра блокировки через блок задержки подключен к одному из входов второго дополнительного элемента И и дополнительного элемента ИЛИ, к другому входу которых подключен выход приемника сигнала «Фаза», а выходы первого и второго дополнительных элементов И и дополнительного элемента

ИЛИ через решающий блок подключены к второму входу перзого элемента И и к входу формирователя сигнала «Ошибка», выход которого подключен к дополнительному входу блока сопряжения.

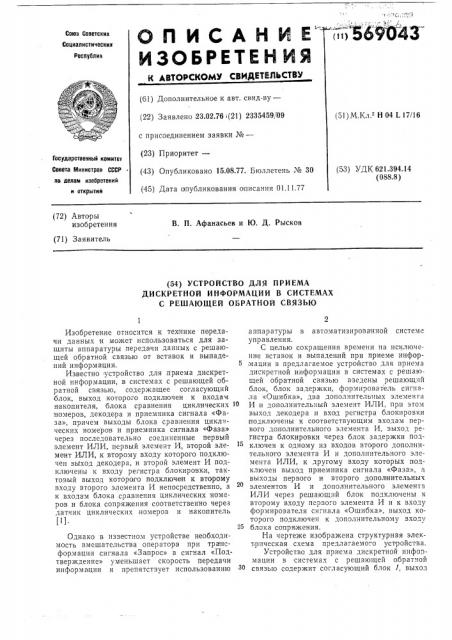

На чертеже изображена структурная электрическая схема предлагаемо о устройства.

Устройство для приема дискретной инфопмации в системах с решающей обратчой связью содержит согласующий блок 1, выход

569043

1О

65 которого подключен к входам накопителя 2, блока 3 сравнения циклических номеров, декодера 4 и приемника 5 сигнала «Фаза», причем выходы блока 8 и приемника 5 через последовательно соединенные первый элемент

ИЛИ б, первый элемент И 7, второй элемент

ИЛИ 8, к второму входу которого подключен выход декодера 4 и второй элемент И 9, подключе|ны к входу регистра блокировки 10, тактовый выход последнего подключен к второму входу второго элемента И 9 непосредственно, а ко входам блоков 8 и 11 сопряжения соответственно через датчик 12 циклических номеров, накопитель 2, решающий блок

18, блок 14 задержки, формирователь 15 сигнала «Ошибка», два дополнительных элемента И 1б и 17 и дополнительчый элемент ИЛИ

18, при этом выход декодера 4,и вход регистра 9 блокировки подключены к соотзстствующим входам перзого дополнительного элемента И 1б, выход регистра 9 блокировки через блок 14 задержки подключен к одному из входов второго дополнительного элемента

И 17 и дополнительного элемента ИЛИ 18, к другому входу которых подключен выход приемника 5, а выходы первого и второго дополнительных элементов Й 1б и 17 и дополнительного элемента ИЛИ 18 через решающий блок 18 подключены к второму входу первого элемента И 7 и к входу формирователя 15, а его выход подключен к дополнительному входу блока 11 сопряжения.

Устройство работает следующим образом.

При обнаружении ошибки в принятой комбинации, несовпадении циклического номера при нятой комбинации ожидаемому или приеме сигнала «Запрос» сигналом с выхода датчика 12 циклических номеров запускается регистр 10 блокировки, сигналами с его выходов стираются и+1 комбинаций с выхода накопителя 2, в течение п+1 циклов запрещается работа датчика 12 цикличвских номеров, а в течение и циклов — запись «1» в регистр 10 блокировки при помощи второго

3JIeмента И 9. Сигналом с выхода декодера

4 одновременно с запуском ре|гистра 10 блокировки через первый дополнительный элемент И 1б на вход решающего блока 18 записывается «1». которая в случае приема сигнала «Запрос» во время блокировки стирается сигналом с выхода приемника 5 через дополнительный элемент ИЛИ 18.

В случае приема сигнала «Запрос» непосредственно после блокировки, вследствие необнаруженного иска жения сигнала «Запрос» ча противоположной станции, сигналом с выхода регистра 10 блокировки запускается блок

14 задержки, с выходов которого выдается два сигнала: первый — в конце анализа комбинации, принимаемой непосредственно после блокировки этим сигналом, в случае, если эта комбинация — сигнал «Запрос», через второй дополнительный элемент И 17 выдается тактовый сигнал, осуществляющий выдачу «1» с выхода решающего блока 13, второй — с задержкой по отношению к первому, не превышающей длительности одного символа, этим сигналом через дополнительный элемент ИЛИ 18 осуществляется стирание «1» в решающем, блоке 13.

Сигналом с выхода решающего блока 18 осуществляется запрет запуска регистра 10 блокировки при помощи первого элемента И 7 и запуск формирователя 15 сигнала «Ошибка», последний выдается на выход устройства через блок 11 со,пряжения.

Предлагаемое устройство позволяет избежать сдвиг информации при необнаруживаемом искажении сигнала «Запрос» в обратном канале, при этом на одной из станций принимается одна комбинация с необнаруженной ошибкой, а на другой — одна комбинация с отметкой «Ошибка», но вставок и выпадений информации не происходит.

Кроме того, устройство для приема дискретной информации в системах с решающей обратной связью позволяет уменьшить время, необходимое для исключения вставок выпадений информации при искажениях служебных сигналов с одновременным увеличением скорости передачи информации.

Формула изобретения

Устройство для приема дискретной информации в системах с решающей обратной связью, содержащее согласующий блок, выход .которого подключен ко входам накопителя, блока сравнения циклических номеров, декодера и приемника сигнала «Фаза», причем выходы блока сравнения циклических номеров и приемника сигнала «Фаза» через последовательно соединенные первый элемент

ИЛИ, первый элемент И, второй элемент

ИЛИ, к второму входу которого подключен выход декодера, и второй элемент И подключены к входу регистра блокировки, тактовый выход которого подключен к второму входу второго элемента И непосредственно, а к входам блока сравнения циклических номеров и блока сопряжения соответственно через датчик циклических номеров и накопитель, отл и ч а ю щ е е с я тем, что, с целью сокраще ния времени на исключение вставок и выпадений при приеме, информации, введены решающий блок, блок задержки, формирователь сигнала «Ошибка», два дополнительных элемента И и дополнительный элемент ИЛИ, при этом выход декодера,и вход регистра блокировки, подключены к соответствующим входам первого дополнительного элемента И, выход регистра блокировки через блок задержки подключен к одному из входов второго дополнительного элемента И и дополнительного элемента ИЛИ, к другому входу которых подключен выход приемника сигнала «Фаза», а выходы первого и второго до569043

Составитель Г. Серова

Техред М. Семенов

Редактор Т. Янова

Корректор В. Гутман

Заказ 653/1702 Изд. № 659 Тираж 818 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, К-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент» полнительных элементов И,и дополнительного элемента ИЛИ через решающий блок подключены к второму входу первого элемента

И и к входу формирователя сигнала «Ошибка», выход которого подключен к дополнительному входу блока сопряжения.

Источник информации, принятый во внимание при экспертизе:

1. Денисов О. Е. Аппаратура передачи данных по телефонным каналам Аккорд

5 1200, «Вопросы радиоэлектроники», серия

Т ПС, вып. б, 1971, с. 32.