Умножитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (») 670064 (61) дополнительное к авт. саид-ву (22) Заявлено23.03.76 (21) 2337621/24 с присоединением заявки № (23) Приоритет (43) Опубликовано25.08.77,Бюллетень %31 (45) Дата опубликования описания 28.00.77 (5l) М. Кл.

Q 06 Q 7/16

Гасударственный комитет

Совета Миннатроа СССР ао делам изооретений и аткро1тий (53) УДК 681.330 (088.8) (72) Авторы изобретения

3. В. Ивановская и В. Т. Рябуха (71) Заявитель

Харьковский институт радиоэлектроники

Изобретение относится к цифровой вычислительной технике.

Известен умножитель частоты следования импульсов низкого и инфракрасного частотных диапазонов с промежуточным врелтя- 5 импульсным преобразователелr, содержащий блок выделепия периода и управления, запо минак>щий;регистр, сумматор, генератор образцовой частоты и вентили переноса (lj.

Наиболее близким технических. решеьптем 1О к изобретению является умножитель, который содержит последовательно вклточ енпы е генератор эталонной частоты, делитель частоты, первый элемент И, регистр, первую группу элементов И, сумматор и элемент

ИЛИ, подсоединенный свободным входом к соответствующему выходу блока управления, два других выхода которого соединены соответственно с управлятощим входом делителя частоты. и потенциальным входом ®О первого элемента И, а вход является входом умножителя (21. Недостатком этих умножителей является их низкая точность

S что обусловлено значительным уровнем паразитной время-импульсной модуляции @ выходных частот, порядка сотен и тысяч герц, вьтзватптой умножением эталонной частоты в дробное число раз.

Белью изобретения является повышение точности умножителя.

Достигается это тем, что умножитель содержит второй и третий элементы И, линию задержки, вторую и третью группы элеметттов И, счетчик, триггер и блок сравнения, первые входы которого соединены с первыми входами элементов И второй группы и с сответствующим выходом блока управления,вторые входы - с выходами разрядов сумматора, а выход подключен к первому входу триггера и к первым входам элементов И третьей группы. Выходы элементов И второй группы подключены к входам соответствующих разрядов сумматора, а их вторые входы — к выходу второго элемента

И, цотенциалытый вход которого соединен с соответствующим выходом блока управления а импульсный вход подклточен к выходу делителя частоты, вторые входы элементов

И третьей группы подсоединены к выходам соответствующих разрядов сумматора, а (54) Ут" тНОШТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

570064 их выходы подключены к установо цым вхс дам счетчика, счетный вход которого подсоединен через третий элемент И к генеpàòîðó эталонной частоты, а выход является выходом умножитепя и соединен с вто- 5 рым входом триггера,,подсоединенного выходом к потенциальному входу третье1 о эпьмента И, вход линии задержки соединен с выходом элемента ИЛИ, а ее выхрд с свободными входами. элементов И первой группы.

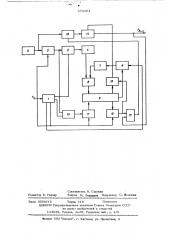

На чертеже дана структурная схема ум.ножитепя частоты следования импульсов.

Умножитепь содержит блок управпения

1, элемент И 2, депитепь частоты 3, регистр5

4, генератор эталонной частоты 5, эпемент

ИЛИ 6, линию задержки 7, группу 8 эпэментов И, сул л1атор 9, элемент И 10, группу 11 элементов И, блок сравнения 12, группу 13 элементов И, счетчик 14, триг- 0 гер 15 и элемент И 16.

У множитель работает следующим образом. Блок управления 1 задает коэффициент умножения K входной. частоты f„ путем подачи разрешающего потенциала на те из

slloMBHToB группы 11 элементов И, через которые каждым выходным импупьсом элемента И 10 в сумматор 9 введется число К на сул м фование. Число К является

30 также коэффициентом деления делителя часс таты 3. Кроме того, код числа К подается на блок сравнения 12.

В процессе работы блок сравнения 12 сравнивает число К с допопннтепьныл1 кодом чисел, образующихся в сумматоре 9.

Импульс на выходе бпока 12 формируется в момент времени, когда в сумматоре 9 будет записано чиспос-д, где с - емкость сумматора 9, b, «< К. В случае д» К

40 илатупьс на выходе блока 12 отсутствует.

Посредством группы 8 элементов 3I осуществляется перенос числа, храняшегося в регистре 4, в сумматор 9; посредством группы 13 элел1ентов И - перенос показа45 ний сумматора 9 в счетчик 14, В исходном состоянии элементы И 2, 10

l6 закрыты запиракшими потенциалами, подаваемыми с блока управления 1 и триггера

15, соответственно, а показания регистра 4, 50 сумматора 9 и счетчика 14-нулевые.

Блоком управпе птя 1 элемент И 2 откры« .вается на один период Т входного сьпнала. х

3а это время с выхода делителя 3 в регистр

4 поступит И» = Т„импульсов, где

- частота генератора 5. Если запись числа И„в регистр 4 осуществляется в допопнитепьном коде, то показания регистра 4 к концу периода Т будут (с — N ) х х где с ел.кость регистра 4, 60

По окончании периода входного сигналя элеллент И 2 закрывается (в дальнейшем блок управления 1 не реагирует на входша . импульсы частоты . Одновременно с л блока управпення 1 на элемент ИЛИ 6 выдается ил1пупьс, который, пройдя через линию задержки 7, посредством группы 8 элементов И 8 осуществляет пеоенос числа (с - К„) из регистра 4 в сумматор 9.

Начиная с второго периода входного сигнала, бпокол4 управпепия 1 открывается элемент И 10. С этого момента каждый выходной ил пульс делитепя 3 посредством группы

11 элементов И параппепьным кодом вводит в сумматор 9 число К, равное коэффициенту умножения, Поскольку совокупность блоков 4, 6, 7, 8, 9 эквивалентна сумматору параллельного типа емкостью N» при поступлении на вход группы 11 эпементов И числа импульсов

Й „на выходе сумматора 9 будет сфор .мировано ровно К импульсов перепопнения и его показания вновь станут равными (С - N ). В дальнейшем описанные про цессы в этой части схел ы будут цикпически повторяться, а на каждые И» входных импульсов группы 11 элементов И на выходе сумматора 9 будет форл ироваться К импульсов, что соответствует умножению частоты 1 „в К раз.

В процессе работы умножитепя каждый выходной ил.пульс сумматора 9 посредством группы 8 элементов И осуществляет запись числа (с — К„) в сумматор 9. В результате показания сумматора 9 после каждого его очередного переполнения и записи числа (с - й„) будут (С - И„ tA„) где A ° - число, оставшееся в сумматове

9 после перепопнения, j = 1,2,3,....,..... переполнения сул;матора 9.

Поскольку А; = К - а; где - остаток от деления - - передпоступнениемна

4 IVY вход группы 11 элементов И ил1пупьса, соответствующего переполнению сумматора 9, в последнем будет записано число (С -ф ), Так как К У-,6 в этот момент на выходе блока сравнения 12 формируется ил пульс, который посредством группы 13 эпементов

И записывает в счетчик 14 число (С -Я )

1 и опрокидывает триггер 15. В результате открывается элемент И 16.

С этого момента импульсы частоты с выхода генератора 5 начинают поступать в счетчик 14 на суммирование. С поступле.нием на его вход д иытупьсов па входе

1 счетчика 14 появится выходной импульс устройства, который, опрокидывая триггер 15, закрывает элемент И 16.

570064

В дальнейшем описанные процессы в схеме циклически повторяются.

Нетрудно видеть, что выходные импульсы умножителя следуют с периодом, определяемым соотношением при этом первое слагаемое правой части последнего cooTHQUIBHHH вырабатывается сумматором о, а второе — счетчиком 14.

Формула изобретения!

Умножитель частоты следования импулт сов, содержащий последоватепьнс вклкченные генератор эталонной частоты, делитель частоты, первый элемент И, регистр, первую группу элементов И, сумматор и > элемент ИЛИ, подсоединенный свободным входом к соответствующему выходу блока управления, два других выхода которого соединены соответственно с управляг щим входом делителя частоты и потенци- у, альиым входом первого элемента И, а вход является входом умчожителя, о т л и ч аю шийся тем, что, с целью повышения точности умножитепя, он содержит второй и третий элементы И, линию задержки, 30 вторую и третью группы элементов И, счет. чик, триггер и блок сравнения, первые входы которого соединены с первыми входами элементов И второй группы и с соотвс:тствуюшим выходом блока управления, вторые входы — с выходами разрядов сук матора, а выход подключен к первому входу триггера и к первым входам элементов И третьей группы, выходы элементов И второй группы подключены ко входам соответствующих разрядов сумматоров, а их вторые входы— к выходу второго элемента И, потенциальный вход которого соединен с соответствующим выходом блока управления, а импульсный вход подключен к выходу делителя частоты, вторые входы элементов И треть-! ей группы подсоединены к выходам соотвгт ствук>ших разрядов сумматора, а их выходы подключены к установочным входам счет» ника, счетный вход которого подсоединен через третий элемент И к генератору эталонной частоты, а выход является выходом умножителя и соединен с вторым входом триггера, подсоединенного выходом к потенциальному входу третьего элемента И, вход линии задержки соединен с выходом элемента ИЛИ, а ее выход со свободными входами элементов И первой группы.

Источники информации, принятые во внимание при экспертизе:

1. Авторско е свид етельство СССР № 320814, Кл. + 06 f 5/00, 1969 °

2. Авторское свидетельтсво СССР

¹ 321819, Кл. Q 06 f 23/10, 1969.

570064

Составитель Н. Сорокин

Редактор Е. Гончар Техред M. Левинская Корректор С. Яь .алова

Заказ 3058/43 Тираж 618 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4