Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

к.оюз Советскнк

Социал исти нескин республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДИТВЛЬСТВУ (6!) Дополнительное к авт. свид-ву (22) Заявлено 14.01.76 (21) 2316474/24 с присоединением заявки № (23) Приоритет(43) Опубликовано25.08.77.Бюллетень м, а 1 (46) Дата опубликования описания Ч0.09. i7 (11) 570109 (51) М. Кл .

Q 11 С 27/00

Гвсудерстевнный квинтет

Вевете Мнннвтрве CGCP ве двлвм изобретений н открытке (53) УДК 681.827.

i;t :,! l „i.i ) (72) Автор изобретения

В; М. Феоктистов (7!) Заявитель (54) АНАЛОГОВОЕ ЗАПОМИНЛ101ЦЕЕ УСТРОЙСТВОИзобретение относится к цифровым системам передачи аналоговой информации, измерительной и другим областям техники, связанным с преобразованием аналоговых сигналов в цифровую форму. б

В связи с широким развитием цифровых систем передачи важное значение приобретает создание аналого-цифровых преобразователей и входящих в их состав устройств выборки и хранения аналоговых сигналов, К служащих для уменьшения динамических ошибок при аналого-цифровом преобразовании.

Известны устройства выборки и хранения, в которых используется явление перезаряда электрического конденсатора от источника 15 входного сигнала во время процесса выборки и сохранение этого заряда на конденсаторе во время процесса хранения аналогового сигнала, _#_, Одним из основных требований, предья- 20 вляемых к устройству, является малый уровень помех на его выходе.

Наиболее близким по технической сущности к изобретению является устройство, содержащее дифференциальный усилитель, вы-2б полненпый на транзисторах и резисторах, на- копительный элемент, например конденсатор, обкладки которого подключены K катодам первых gHogoB и выходам устройства соответственно, шину управляющих импульсов, шину постоянного напряжения(т .

Недостатком известного устройства является влияние Ei8 характеристики выходного сигнала помех, воздействующих на его вход, Q также общие де питания, цепи уцра» пения процессамп выборки и хранения этого устройства. Это обусловлено тем, что помеха, которая образовалась в общей цепи питания или на входе ключевого каскада, проходит на выход устройства во время выборки входного сигнала, так как конденсатор, на котором запоминается входной сигнал, включен несимметрично Ilo отношению и этим цепям, а именно между общей точкой соединения двух диодов и обшей точкой устройства. Кроме того, в известном устройстве помехи, действуюнще на входе устрой ства, также проходят па его выход, так как два усилительных каскада, подключенных K выходам цифференциальноги каскада, имеют

5701

3 малый коэффициент подавления синфазной помехи.

Целью изобретения является повьпнение помехоустойчивости устройства.

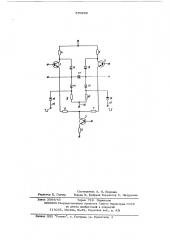

Достигается это благодаря тому, что в устройство введены вторые и третьи диоды и дополнительные резисторы, причем аноды третьих диодов подключены к обкладкам кон

geHcBTopa, в катоды — к катодам ° вторых диомов и через допрлнительные резисторы к шине постоянного напряжения; аноды вт рых диодов соединены с шиной управляющих импульсов, Не чертеже дана электрическая схема предлагаемого устройства.

Аналоговое запоминающее устройство содержит дифференциальный усилитель, вынолненный на транзисторах 1-3, резисторы

4-10, диоды 11-16 и конденсатор 17, шину постоянного напряжения 18, шину управ- 20 ляккпих импульсов 19.

Работа устройства происходит следующим образом. Во время процесса выборки на шину управляющих импульсов устройства постуцают два идентичных о"рицательных импуль- 2 св управления, которые обеспечивают обратное смещение диодов 15 и 16. При этом ток от источника питания, протекая через резисторы 4, 5, диоды 11-14 и резисторы 9, 10, смешает диоды 11-14 в прямом gp направлении. Благодаря етому конденсатор 17 заряжается до величины выходного напряl-.ения дифференциального усилителя с постоянной времени .1 С(г +2г ) где С - величина емкости конденсатора 17; в,„- выходное сопротивление дифференциального каскада; р„ — динамическое сопротивле..ие диодов 40

11, 12.

Для того, ч"îáû резисторы 9, 10 нэ шуктироввли, конденсатор 17 во время его переэвряда, величина сопротивлений этих резисторов должна быть намного больше выходного сопротивления дифференциального каскада вык.

Во время процесса хранения аналогового сигнала кв шине управляющих импульсов при- О сутствуют положительные потенциалы, которые обеспе обратное смешение диодов 11- 14. При этом конденсатор 17 оказывается изолированным как от выхода дифференциальногo усилителя, так и от резисто-g5

09

4 ров S, 10, благодаря чему обеспечивается сохранение на конденсаторе 17 заряда, полученного во время выборки.

Ток утечки конденсатора 17 во время хранения аналогового сигнала зависит от величин сопротивлений, выключенных диодов

11-14, Предложенное устройство по сравнению с известными уменьшает влияние нв характеристики выходного сигнала помех, воздействующих нв его вход, а также на общие цепи питания и цепи управления процессами выборки и хранения аналогового сигнала, так . квк конденсатор, нв котором запоминается входной сигнал, включен через два идентичных диода между выходами дифференциального усил "-теля, а источни сигнала упввления включен симметрично по отношению двум обкладкам конденсатора, с которых снимается выходной сигнал, При этом помехи, которые присутствуют на сигнальных входах устройства, общих цепях питания и управляющих входах устройства оказываются синфазнымй на обкладка" конденсатора, с которых снимается выходной сигнал, что п„иводит к уменьшению уровня помех на выходе устройства по сравнению с известными устройствами.

Формула изобретения

Аналоговое запоминающее устройство„ содержащее дифференциальный усилитель, выполненный нв транзисторах и резисторах, накопительный элемент, например конденсатор, обкладки которого подключены к катодам первых диодов и выходам устройства соответственно, шину управляющих импульсов, шину постоянного напряжения, о т л ич а ю щ е е с я тем, что, с целью повышения помехоустойчивости устройства, в него введены вторые и третьи диоды и дополнительные резисторы, причем аноды третьих диодов подключены к обкладкам конденсатора, в катоды — к катодам вторых диодов и через дополнительные резисторы к шине постоянного напряжения, аноды вторых диодов соединены шиной управляющих импульсов.

Источники информации, принятые во вниманив при экспертизе:

1. Заявка Японии М 49-21744, кл.

98(5} Д З1, 1974

Составитель А. П. Воронин

Е едактор E. Гончар Гехред H. Бабурка Корректор С. Патрушева

Эаеаз 3064/45 Тираж 729 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Х13035, Москва, Ж»З5, Раушская наб., д. 4/Ь

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4